- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4200 > XCV1600E-6FG900C (Xilinx Inc)IC FPGA 1.8V C-TEMP 900-FBGA PDF資料下載

參數(shù)資料

| 型號(hào): | XCV1600E-6FG900C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 112/233頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 1.8V C-TEMP 900-FBGA |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | Virtex®-E |

| LAB/CLB數(shù): | 7776 |

| 邏輯元件/單元數(shù): | 34992 |

| RAM 位總計(jì): | 589824 |

| 輸入/輸出數(shù): | 700 |

| 門(mén)數(shù): | 2188742 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類(lèi)型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 900-BBGA |

| 供應(yīng)商設(shè)備封裝: | 900-FBGA |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)當(dāng)前第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)第124頁(yè)第125頁(yè)第126頁(yè)第127頁(yè)第128頁(yè)第129頁(yè)第130頁(yè)第131頁(yè)第132頁(yè)第133頁(yè)第134頁(yè)第135頁(yè)第136頁(yè)第137頁(yè)第138頁(yè)第139頁(yè)第140頁(yè)第141頁(yè)第142頁(yè)第143頁(yè)第144頁(yè)第145頁(yè)第146頁(yè)第147頁(yè)第148頁(yè)第149頁(yè)第150頁(yè)第151頁(yè)第152頁(yè)第153頁(yè)第154頁(yè)第155頁(yè)第156頁(yè)第157頁(yè)第158頁(yè)第159頁(yè)第160頁(yè)第161頁(yè)第162頁(yè)第163頁(yè)第164頁(yè)第165頁(yè)第166頁(yè)第167頁(yè)第168頁(yè)第169頁(yè)第170頁(yè)第171頁(yè)第172頁(yè)第173頁(yè)第174頁(yè)第175頁(yè)第176頁(yè)第177頁(yè)第178頁(yè)第179頁(yè)第180頁(yè)第181頁(yè)第182頁(yè)第183頁(yè)第184頁(yè)第185頁(yè)第186頁(yè)第187頁(yè)第188頁(yè)第189頁(yè)第190頁(yè)第191頁(yè)第192頁(yè)第193頁(yè)第194頁(yè)第195頁(yè)第196頁(yè)第197頁(yè)第198頁(yè)第199頁(yè)第200頁(yè)第201頁(yè)第202頁(yè)第203頁(yè)第204頁(yè)第205頁(yè)第206頁(yè)第207頁(yè)第208頁(yè)第209頁(yè)第210頁(yè)第211頁(yè)第212頁(yè)第213頁(yè)第214頁(yè)第215頁(yè)第216頁(yè)第217頁(yè)第218頁(yè)第219頁(yè)第220頁(yè)第221頁(yè)第222頁(yè)第223頁(yè)第224頁(yè)第225頁(yè)第226頁(yè)第227頁(yè)第228頁(yè)第229頁(yè)第230頁(yè)第231頁(yè)第232頁(yè)第233頁(yè)

Virtex-E 1.8 V Field Programmable Gate Arrays

R

Module 1 of 4

DS022-1 (v3.0) March 21, 2014

2

Production Product Specification

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

Virtex-E Compared to Virtex Devices

The Virtex-E family offers up to 43,200 logic cells in devices

up to 30% faster than the Virtex family.

I/O performance is increased to 622 Mb/s using Source

Synchronous data transmission architectures and synchro-

nous system performance up to 240 MHz using sin-

gled-ended SelectI/O technology. Additional I/O standards

are supported, notably LVPECL, LVDS, and BLVDS, which

use two pins per signal. Almost all signal pins can be used

for these new standards.

Virtex-E devices have up to 640 Kb of faster (250 MHz)

block SelectRAM, but the individual RAMs are the same

size and structure as in the Virtex family. They also have

eight DLLs instead of the four in Virtex devices. Each indi-

vidual DLL is slightly improved with easier clock mirroring

and 4x frequency multiplication.

VCCINT, the supply voltage for the internal logic and mem-

ory, is 1.8 V, instead of 2.5 V for Virtex devices. Advanced

processing and 0.18

μm design rules have resulted in

smaller dice, faster speed, and lower power consumption.

I/O pins are 3 V tolerant, and can be 5 V tolerant with an

external 100

Ω resistor. PCI 5 V is not supported. With the

addition of appropriate external resistors, any pin can toler-

ate any voltage desired.

Banking rules are different. With Virtex devices, all input

buffers are powered by VCCINT. With Virtex-E devices, the

LVTTL, LVCMOS2, and PCI input buffers are powered by

the I/O supply voltage VCCO.

The Virtex-E family is not bitstream-compatible with the Vir-

tex family, but Virtex designs can be compiled into equiva-

lent Virtex-E devices.

The same device in the same package for the Virtex-E and

Virtex families are pin-compatible with some minor excep-

tions. See the data sheet pinout section for details.

General Description

The Virtex-E FPGA family delivers high-performance,

high-capacity programmable logic solutions. Dramatic

increases in silicon efficiency result from optimizing the new

architecture for place-and-route efficiency and exploiting an

aggressive 6-layer metal 0.18

μm CMOS process. These

advances make Virtex-E FPGAs powerful and flexible alter-

natives to mask-programmed gate arrays. The Virtex-E fam-

ily includes the nine members in Table 1.

Building on experience gained from Virtex FPGAs, the

Virtex-E family is an evolutionary step forward in program-

mable logic design. Combining a wide variety of program-

mable system features, a rich hierarchy of fast, flexible

interconnect resources, and advanced process technology,

the Virtex-E family delivers a high-speed and high-capacity

programmable logic solution that enhances design flexibility

while reducing time-to-market.

Virtex-E Architecture

Virtex-E devices feature a flexible, regular architecture that

comprises an array of configurable logic blocks (CLBs) sur-

rounded by programmable input/output blocks (IOBs), all

interconnected by a rich hierarchy of fast, versatile routing

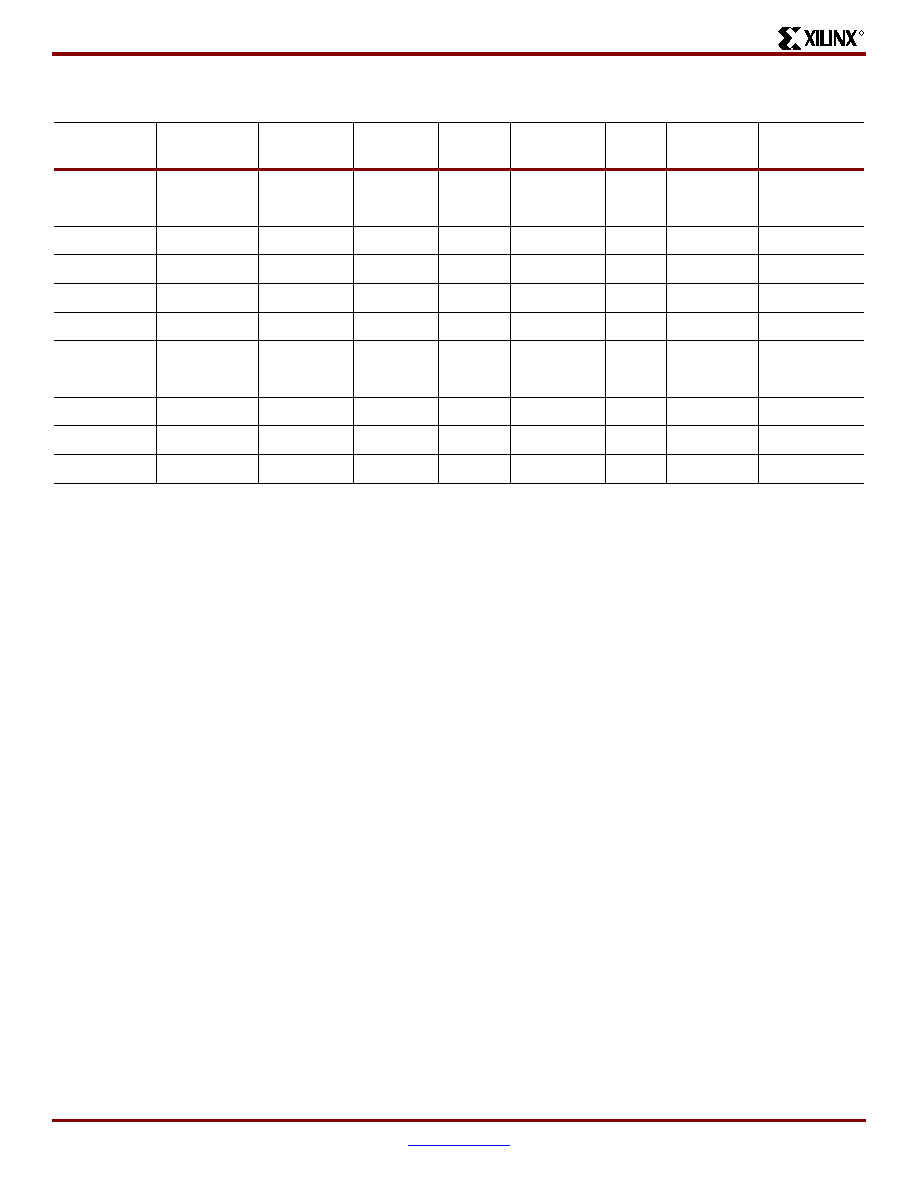

Table 1: Virtex-E Field-Programmable Gate Array Family Members

Device

System

Gates

Logic

Gates

CLB

Array

Logic

Cells

Differential

I/O Pairs

User

I/O

BlockRAM

Bits

Distributed

RAM Bits

XCV50E

71,693

20,736

16 x 24

1,728

83

176

65,536

24,576

XCV100E

128,236

32,400

20 x 30

2,700

83

196

81,920

38,400

XCV200E

306,393

63,504

28 x 42

5,292

119

284

114,688

75,264

XCV300E

411,955

82,944

32 x 48

6,912

137

316

131,072

98,304

XCV400E

569,952

129,600

40 x 60

10,800

183

404

163,840

153,600

XCV600E

985,882

186,624

48 x 72

15,552

247

512

294,912

221,184

XCV1000E

1,569,178

331,776

64 x 96

27,648

281

660

393,216

XCV1600E

2,188,742

419,904

72 x 108

34,992

344

724

589,824

497,664

XCV2000E

2,541,952

518,400

80 x 120

43,200

344

804

655,360

614,400

XCV2600E

3,263,755

685,584

92 x 138

57,132

344

804

753,664

812,544

XCV3200E

4,074,387

876,096

104 x 156

73,008

344

804

851,968

1,038,336

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC6VLX365T-2FFG1156C | IC FPGA VIRTEX 6 364K 1156FFGBGA |

| W25Q64FVZPIG | IC SPI FLASH 64MBIT 8WSON |

| XC5VFX100T-1FF1738I | IC FPGA VIRTEX-5FXT 1738FFBGA |

| XC5VFX100T-1FFG1738I | IC FPGA VIRTEX 5 100K 1738FFGBGA |

| IDT71024S12YGI | IC SRAM 1MBIT 12NS 32SOJ |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV1600E-6FG900I | 功能描述:IC FPGA 1.8V I-TEMP 900-FBGA RoHS:否 類(lèi)別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:Virtex®-E 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標(biāo)準(zhǔn)包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計(jì):3200 輸入/輸出數(shù):80 門(mén)數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類(lèi)型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應(yīng)商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XCV1600E-6HQ240C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

| XCV1600E-6HQ240I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

| XCV1600E-7BG240C | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex⑩-E 1.8 V Field Programmable Gate Arrays |

| XCV1600E-7BG240I | 制造商:XILINX 制造商全稱(chēng):XILINX 功能描述:Virtex-E 1.8 V Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。