- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4142 > XCS40-4PQ208C (Xilinx Inc)IC FPGA 5V C-TEMP 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | XCS40-4PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 8/83頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 5V C-TEMP 208-PQFP |

| 產(chǎn)品變化通告: | Spartan,Virtex FPGA/SCD Discontinuation 18/Oct/2010 |

| 標(biāo)準(zhǔn)包裝: | 24 |

| 系列: | Spartan® |

| LAB/CLB數(shù): | 784 |

| 邏輯元件/單元數(shù): | 1862 |

| RAM 位總計: | 25088 |

| 輸入/輸出數(shù): | 169 |

| 門數(shù): | 40000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當(dāng)前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

Spartan and Spartan-XL FPGA Families Data Sheet

16

DS060 (v2.0) March 1, 2013

Product Specification

R

Product Obsolete/Under Obsolescence

CLB signals from which they are originally derived are

shown in Table 10.

The RAM16X1D primitive used to instantiate the dual-port

RAM consists of an upper and a lower 16 x 1 memory array.

The address port labeled A[3:0] supplies both the read and

write addresses for the lower memory array, which behaves

the same as the 16 x 1 single-port RAM array described

previously. Single Port Out (SPO) serves as the data output

for the lower memory. Therefore, SPO reflects the data at

address A[3:0].

The other address port, labeled DPRA[3:0] for Dual Port

Read Address, supplies the read address for the upper

memory. The write address for this memory, however,

comes from the address A[3:0]. Dual Port Out (DPO) serves

as the data output for the upper memory. Therefore, DPO

reflects the data at address DPRA[3:0].

By using A[3:0] for the write address and DPRA[3:0] for the

read address, and reading only the DPO output, a FIFO that

can read and write simultaneously is easily generated. The

simultaneous

read/write

capability

possible

with

the

dual-port RAM can provide twice the effective data through-

put of a single-port RAM alternating read and write opera-

tions.

The timing relationships for the dual-port RAM mode are

shown in Figure 13.

Note that write operations to RAM are synchronous

(edge-triggered); however, data access is asynchronous.

Initializing RAM at FPGA Configuration

Both RAM and ROM implementations in the Spartan/XL

families are initialized during device configuration. The initial

contents are defined via an INIT attribute or property

attached to the RAM or ROM symbol, as described in the

library guide. If not defined, all RAM contents are initialized

to zeros, by default.

RAM initialization occurs only during device configuration.

The RAM content is not affected by GSR.

More Information on Using RAM Inside CLBs

Three application notes are available from Xilinx that dis-

cuss synchronous (edge-triggered) RAM: "Xilinx Edge-Trig-

gered and Dual-Port RAM Capability," "Implementing FIFOs

in Xilinx RAM," and "Synchronous and Asynchronous FIFO

Designs." All three application notes apply to both the Spar-

tan and the Spartan-XL families.

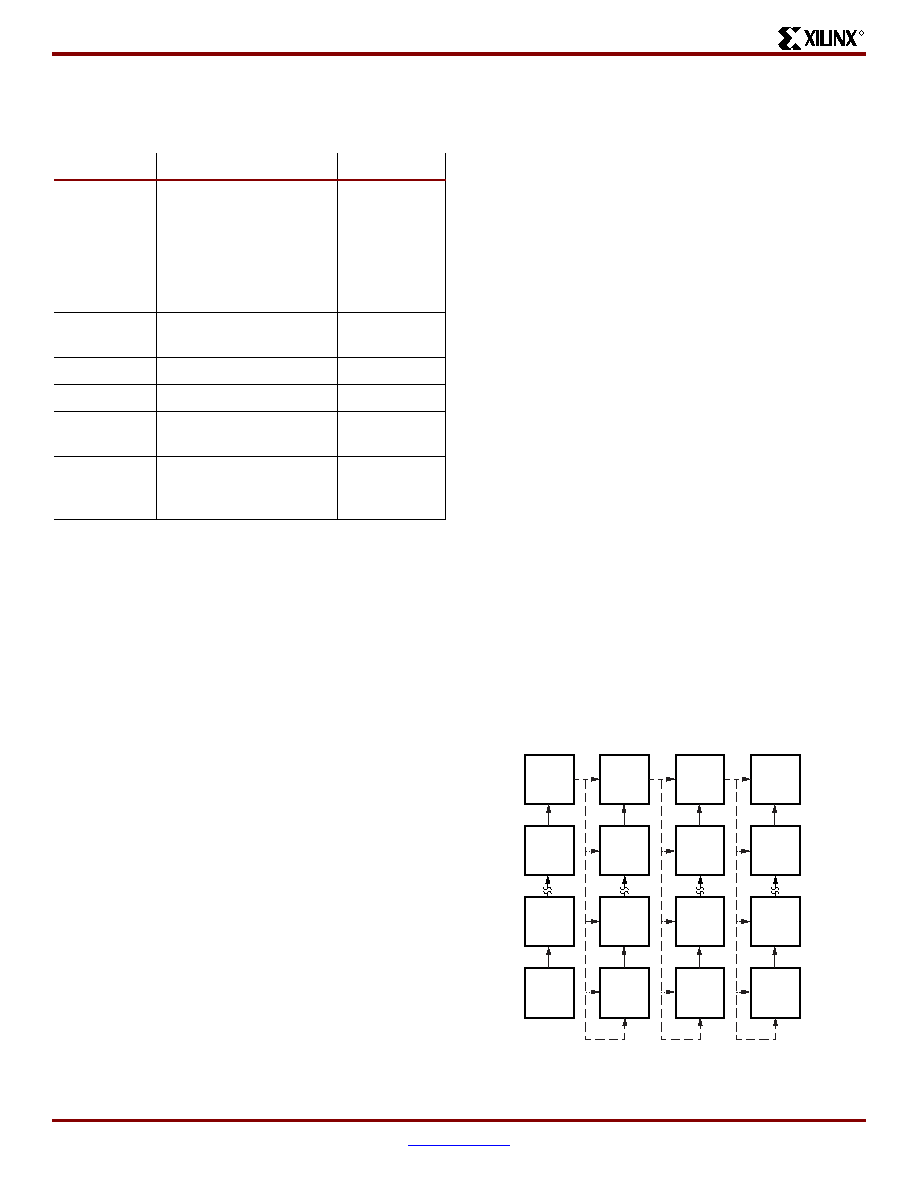

Fast Carry Logic

Each CLB F-LUT and G-LUT contains dedicated arithmetic

logic for the fast generation of carry and borrow signals.

This extra output is passed on to the function generator in

the adjacent CLB. The carry chain is independent of normal

routing resources. (See Figure 15.)

Dedicated fast carry logic greatly increases the efficiency

and performance of adders, subtractors, accumulators,

comparators and counters. It also opens the door to many

new applications involving arithmetic operation, where the

previous generations of FPGAs were not fast enough or too

inefficient. High-speed address offset calculations in micro-

processor or graphics systems, and high-speed addition in

digital signal processing are two typical applications.

The two 4-input function generators can be configured as a

2-bit adder with built-in hidden carry that can be expanded

to any length. This dedicated carry circuitry is so fast and

efficient that conventional speed-up methods like carry gen-

erate/propagate are meaningless even at the 16-bit level,

and of marginal benefit at the 32-bit level. This fast carry

logic is one of the more significant features of the Spartan

Table 10: Dual-Port RAM Signals

RAM Signal

Function

CLB Signal

D

Data In

DIN

A[3:0]

Read Address for

Single-Port.

Write Address for

Single-Port and

Dual-Port.

F[4:1]

DPRA[3:0]

Read Address for

Dual-Port

G[4:1]

WE

Write Enable

SR

WCLK

Clock

K

SPO

Single Port Out

(addressed by A[3:0])

FOUT

DPO

Dual Port Out

(addressed by

DPRA[3:0])

GOUT

Figure 15: Available Spartan/XL Carry Propagation

Paths

CLB

DS060_15_081100

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| FMC26DRYS-S93 | CONN EDGECARD 52POS .100 DIP SLD |

| XCS40-4BG256C | IC FPGA 5V C-TEMP 256-PBGA |

| HMC49DRAS-S734 | CONN EDGECARD 98POS .100 R/A PCB |

| RSC43DTEI | CONN EDGECARD 86POS .100 EYELET |

| XCS40-3PQ240C | IC FPGA 5V C-TEMP 240-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS40-4PQ208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-4PQ240C | 功能描述:IC FPGA 5V C-TEMP 240-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan® 標(biāo)準(zhǔn)包裝:1 系列:Kintex-7 LAB/CLB數(shù):25475 邏輯元件/單元數(shù):326080 RAM 位總計:16404480 輸入/輸出數(shù):350 門數(shù):- 電源電壓:0.97 V ~ 1.03 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:900-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:900-FCBGA(31x31) 其它名稱:122-1789 |

| XCS40-4PQ240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-4PQ256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS40-4PQ256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。