- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄300156 > XCS30-5VQ240I (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號(hào): | XCS30-5VQ240I |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴達(dá)和Spartan - xL的家庭現(xiàn)場(chǎng)可編程門陣列 |

| 文件頁(yè)數(shù): | 1/82頁(yè) |

| 文件大?。?/td> | 863K |

| 代理商: | XCS30-5VQ240I |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)

DS060 (v1.6) September 19, 2001

1

Product Specification

1-800-255-7778

2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Introduction

The Spartan and the Spartan-XL families are a high-vol-

ume production FPGA solution that delivers all the key

requirements for ASIC replacement up to 40,000 gates.

These requirements include high performance, on-chip

RAM, core solutions and prices that, in high volume,

approach and in many cases are equivalent to mask pro-

grammed ASIC devices.

The Spartan series is the result of more than 14 years of

FPGA design experience and feedback from thousands of

customers. By streamlining the Spartan series feature set,

leveraging advanced process technologies and focusing on

total cost management, the Spartan series delivers the key

features required by ASIC and other high-volume logic

users while avoiding the initial cost, long development

cycles and inherent risk of conventional ASICs. The Spar-

tan and Spartan-XL families in the Spartan series have ten

members, as shown in Table 1.

Spartan and Spartan-XL Features

Note: The Spartan series devices described in this data

sheet include the 5V Spartan family and the 3.3V

Spartan-XL family. See the separate data sheet for the 2.5V

Spartan-II family.

First ASIC replacement FPGA for high-volume

production with on-chip RAM

Density up to 1862 logic cells or 40,000 system gates

Streamlined feature set based on XC4000 architecture

System performance beyond 80 MHz

Broad set of AllianceCORE and LogiCORE

predefined solutions available

Unlimited reprogrammability

Low cost

System level features

-

Available in both 5V and 3.3V versions

-

On-chip SelectRAM memory

-

Fully PCI compliant

-

Full readback capability for program verification

and internal node observability

-

Dedicated high-speed carry logic

-

Internal 3-state bus capability

-

Eight global low-skew clock or signal networks

-

IEEE 1149.1-compatible Boundary Scan logic

-

Low cost plastic packages available in all densities

-

Footprint compatibility in common packages

Fully supported by powerful Xilinx development system

-

Foundation Series: Integrated, shrink-wrap

software

-

Alliance Series: Dozens of PC and workstation

third party development systems supported

-

Fully automatic mapping, placement and routing

Additional Spartan-XL Features

3.3V supply for low power with 5V tolerant I/Os

Power down input

Higher performance

Faster carry logic

More flexible high-speed clock network

Latch capability in Configurable Logic Blocks

Input fast capture latch

Optional mux or 2-input function generator on outputs

12 mA or 24 mA output drive

5V and 3.3V PCI compliant

Enhanced Boundary Scan

Express Mode configuration

Chip scale packaging

0

Spartan and Spartan-XL Families

Field Programmable Gate Arrays

DS060 (v1.6) September 19, 2001

00

Product Specification

R

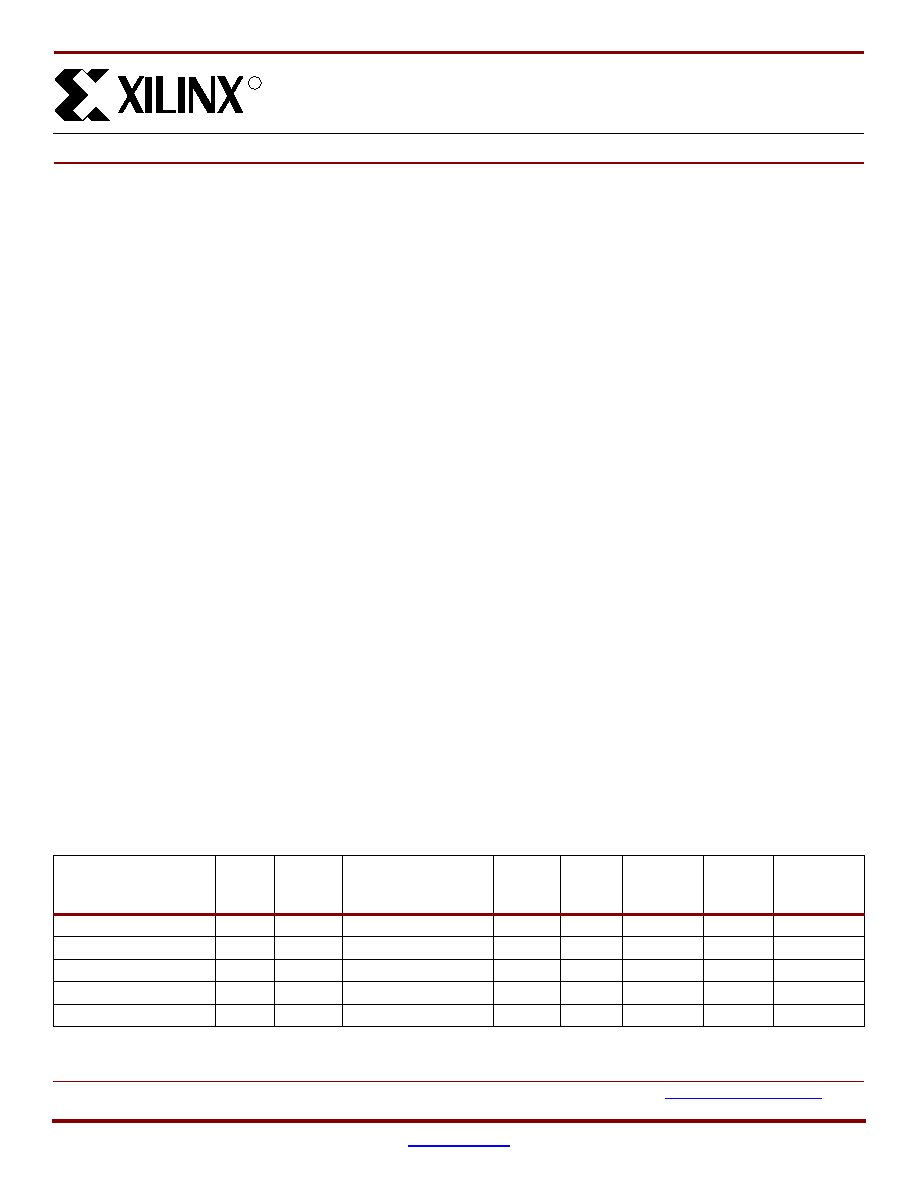

Table 1: Spartan and Spartan-XL Field Programmable Gate Arrays

Device

Logic

Cells

Max

System

Gates

Typical

Gate Range

(Logic and RAM)(1)

CLB

Matrix

Total

CLBs

No. of

Flip-flops

Max.

Avail.

User I/O

Total

Distributed

RAM Bits

XCS05 and XCS05XL

238

5,000

2,000-5,000

10 x 10

100

360

77

3,200

XCS10 and XCS10XL

466

10,000

3,000-10,000

14 x 14

196

616

112

6,272

XCS20 and XCS20XL

950

20,000

7,000-20,000

20 x 20

400

1,120

160

12,800

XCS30 and XCS30XL

1368

30,000

10,000-30,000

24 x 24

576

1,536

192

18,432

XCS40 and XCS40XL

1862

40,000

13,000-40,000

28 x 28

784

2,016

224

25,088

Notes:

1.

Max values of Typical Gate Range include 20-30% of CLBs used as RAM.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCS30-5VQ256C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ256I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ280C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ280I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ84I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS30-5VQ256C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ256I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ280C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ280I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS30-5VQ84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。