- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372886 > XCS05XL-3PC144C (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號: | XCS05XL-3PC144C |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴達(dá)和Spartan - xL的家庭現(xiàn)場可編程門陣列 |

| 文件頁數(shù): | 5/66頁 |

| 文件大小: | 809K |

| 代理商: | XCS05XL-3PC144C |

第1頁第2頁第3頁第4頁當(dāng)前第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

R

DS060 (v1.5) March 2, 2000

Powered by ICminer.com Electronic-Library Service CopyRight 2003

4-5

Spartan and Spartan-XL Families Field Programmable Gate Arrays

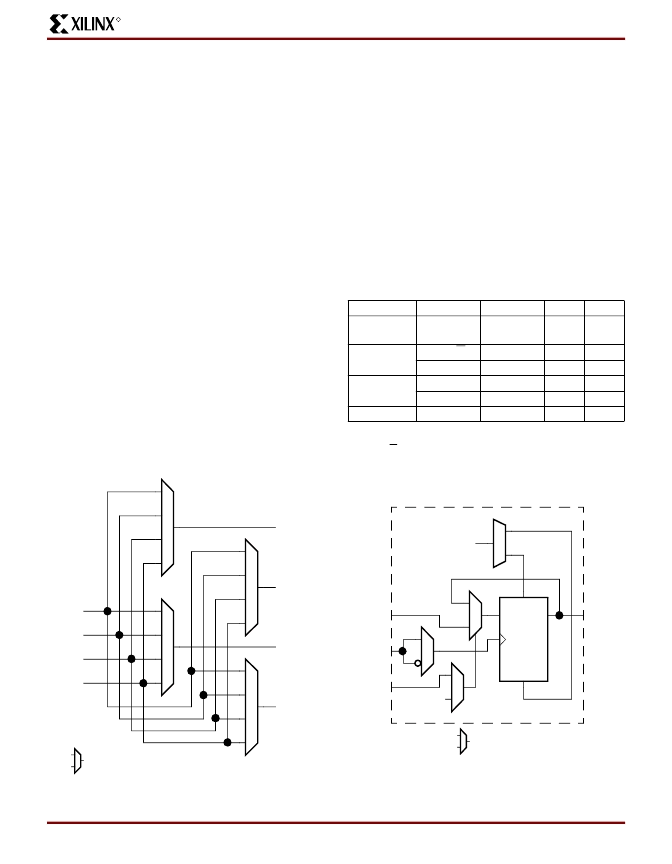

CLB Signal Flow Control

In addition to the H-LUT input control multiplexers (shown

in box "A" of

Figure 2 on page 3

) there are signal flow con-

trol multiplexers (shown in box "B" of

Figure 2

) which select

the signals which drive the flip-flop inputs and the combina-

torial CLB outputs (X and Y).

Each flip-flop input is driven from a 4:1 multiplexer which

selects among the three LUT outputs and DIN as the data

source.

Each combinatorial output is driven from a 2:1 multiplexer

which selects between two of the LUT outputs. The X out-

put can be driven from the F-LUT or H-LUT, the Y output

from G-LUT or H-LUT.

Control Signals

There are four signal control multiplexers on the input of the

CLB. These multiplexers allow the internal CLB control sig-

nals (H1, DIN, SR, and EC in

Figure 2

and

Figure 4

) to be

driven from any of the four general control inputs (C1 - C4

in

Figure 4

) into the CLB. Any of these inputs can drive any

of the four internal control signals.

The four internal control signals are:

EC - Enable Clock

SR - Asynchronous Set/Reset or H function generator

Input 0

DIN - Direct In or H function generator Input 2

H1 - H function generator Input 1.

Input/Output Blocks (IOBs)

User-configurable input/output blocks (IOBs) provide the

interface between external package pins and the internal

logic. Each IOB controls one package pin and can be con-

figured for input, output, or bidirectional signals.

Figure 5 on

page 6

shows a simplified functional block diagram of the

Spartan/XL IOB.

IOB Input Signal Path

The input signal to the IOB can be configured to either go

directly to the routing channels (via I1 and I2 in

Figure 5

) or

to the input register. The input register can be programmed

as either an edge-triggered flip-flop or a level-sensitive

latch. The functionality of this register is shown in

Table 3

,

and a simplified block diagram of the register can be seen

in

Figure 6

.

Figure 4: CLB Control Signal Interface

C1

C2

C3

C4

DIN

H1

SR

EC

Multiplexer Controlled

by Configuration Program

Rev 1.1

Table 3: Input Register Functionality

Mode

CK

X

EC

X

D

X

Q

SR

Power-Up or

GSR

Flip-Flop

__/

0

1

0

X

1*

X

1*

1*

0

D

X

X

D

X

D

Q

Q

D

Q

Latch

Both

Legend:

X

__/

SR

0*

1*

Don

’

t care

Rising edge (clock not inverted)

Set or Reset value. Reset is default.

Input is Low or unconnected (default value)

Input is High or unconnected (default value)

D

Q

SD

RD

GSR

D

EC

CK

Q

Multiplexer Controlled

by Configuration Program

Rev 1.1

Vcc

Figure 6: IOB Flip-Flop/Latch Functional Block

Diagram

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCS05XL-3PC144I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC208I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC240C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC240I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC256C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS05XL-3PC144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05XL-3PC240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。