- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372886 > XCS05-3BG280C (Xilinx, Inc.) Spartan and Spartan-XL Families Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號(hào): | XCS05-3BG280C |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| 中文描述: | 斯巴達(dá)和Spartan - xL的家庭現(xiàn)場可編程門陣列 |

| 文件頁數(shù): | 3/66頁 |

| 文件大?。?/td> | 809K |

| 代理商: | XCS05-3BG280C |

第1頁第2頁當(dāng)前第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁

R

DS060 (v1.5) March 2, 2000

Powered by ICminer.com Electronic-Library Service CopyRight 2003

4-3

Spartan and Spartan-XL Families Field Programmable Gate Arrays

Logic Functional Description

The Spartan series uses a standard FPGA structure as

shown in

Figure 1 on page 2

. The FPGA consists of an

array of configurable logic blocks (CLBs) placed in a matrix

of routing channels. The input and output of signals is

achieved through a set of input/output blocks (IOBs) form-

ing a ring around the CLBs and routing channels.

CLBs provide the functional elements for implementing

the user

’

s logic.

IOBs provide the interface between the package pins

and internal signal lines.

Routing channels provide paths to interconnect the

inputs and outputs of the CLBs and IOBs.

The functionality of each circuit block is customized during

configuration by programming internal static memory cells.

The values stored in these memory cells determine the

logic functions and interconnections implemented in the

FPGA.

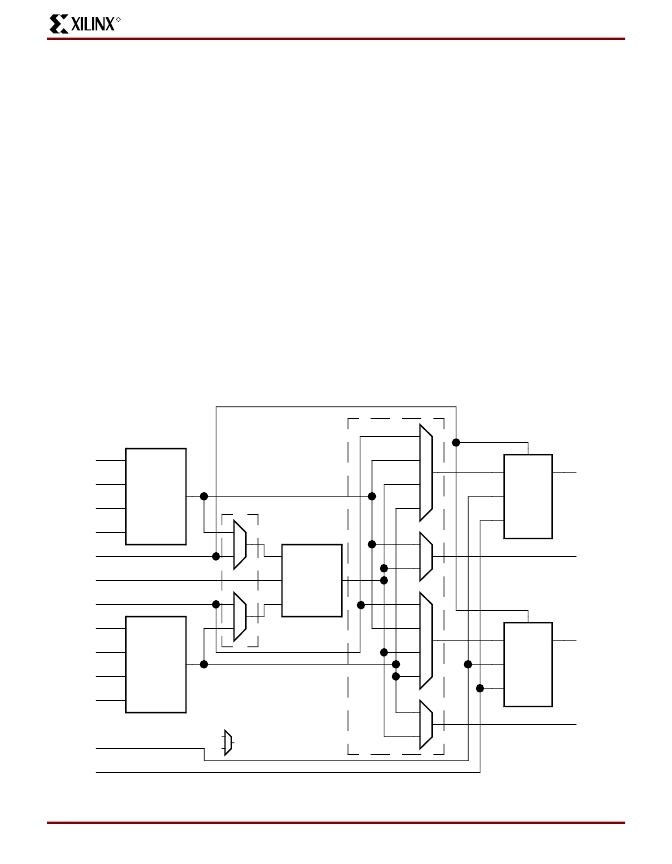

Configurable Logic Blocks (CLBs)

The CLBs are used to implement most of the logic in an

FPGA. The principal CLB elements are shown in the simpli-

fied block diagram in

Figure 2

. There are three look-up

tables (LUT) which are used as logic function generators,

two flip-flops and two groups of signal steering multiplexers.

There are also some more advanced features provided by

the CLB which will be covered in the

“

Advanced Features

Description

”

on page 12

.

Function Generators

Two 16 x 1 memory look-up tables (F-LUT and G-LUT) are

used to implement 4-input function generators, each offer-

ing unrestricted logic implementation of any Boolean func-

tion of up to four independent input signals (F1 to F4 or G1

to G4). Using memory look-up tables the propagation delay

is independent of the function implemented.

A third 3-input function generator (H-LUT) can implement

any Boolean function of its three inputs. Two of these inputs

are controlled by programmable multiplexers (see box "A"

of

Figure 2

). These inputs can come from the F-LUT or

G-LUT outputs or from CLB inputs. The third input always

comes from a CLB input. The CLB can, therefore, imple-

ment certain functions of up to nine inputs, like parity

checking. The three LUTs in the CLB can also be combined

to do any arbitrarily defined Boolean function of five inputs.

Figure 2: Spartan/XL Simplified CLB Logic Diagram (some features not shown)

XQ

Y

YQ

X

DIN

EC

G4

G3

G2

G1

H1

SR

K

Multiplexer Controlled

by Configuration Program

Rev 1.0

Logic

Function

of

F,G,H1

G

H1

F

H

F4

F3

F2

F1

F-LUT

G-LUT

H-LUT

A

B

Logic

Function

of

G1-G4

G4

G3

G2

G1

G

EC

D

Q

SR

CK

EC

D

Q

SR

CK

Logic

Function

of

F1-F4

F4

F3

F2

F1

F

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCS05-3BG280I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3BG84C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3BG84I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3CS100C | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3CS100I | Spartan and Spartan-XL Families Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCS05-3BG280I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3BG84C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3BG84I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3CS100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

| XCS05-3CS100I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan and Spartan-XL Families Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。