- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372880 > XCCACESERIES System ACE CompactFlash Solution PDF資料下載

參數(shù)資料

| 型號: | XCCACESERIES |

| 英文描述: | System ACE CompactFlash Solution |

| 中文描述: | 系統(tǒng)ACE CF卡解決方案 |

| 文件頁數(shù): | 4/29頁 |

| 文件大小: | 285K |

| 代理商: | XCCACESERIES |

第1頁第2頁第3頁當(dāng)前第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁

R

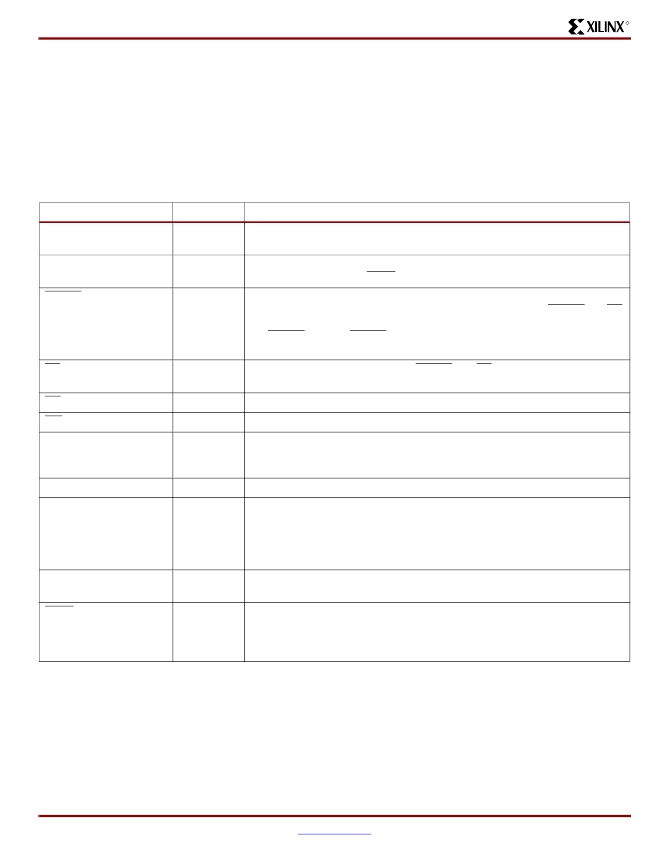

Pin Descriptions

This section provides native Flash interface, Boundary

Scan, and target FPGA configuration pinout information.

Native Flash Interface Pins

All of the native Flash memory pins are routed to pins on the

System ACE MPM ball-grid-array. Thus, the Flash memory

is available to the system for direct read and write access

with a few restrictions. See Note 1 and

Table 1

for descrip-

tions of the restrictions.

Notes:

1.

All of the native Flash memory interface pins are connected to

the System ACE MPM controller (except where explicitly

noted in the pin description). The FCM_ENABLE pin must be

held Low to externally access the Flash memory without

contention with the System ACE MPM controller.

Boundary Scan Pins

The System ACE MPM controller (Virtex-E XCV50E) and

the System ACE MPM controller PROM (XC18V01) are

both IEEE Standard 1149.1 compatible devices. The Sys-

tem ACE MPM connects these devices into an internal scan

chain comprised of the XC18V01 device followed by the

XCV50E device. The internal scan chain is accessible

through the boundary scan test access port (TAP) on the

BG388 package. See

Table 2

.

Table 1:

Native Flash Memory Interface Pins

Pin Name

Pin Type

Description

A0-A21

I/O

Flash memory address bus. A21 exists on the XCCACEM64 only. A20 exists

on the XCCACEM32 and XCCACEM64 only.

DQ0-DQ15

I/O

Flash memory data bus. DQ15 becomes the A-1 pin in the XCCACEM16 and

XCCACEM32 when the BYTE mode is active.

RESET

I/O

Flash memory hardware reset. When asserted, all Flash operations are

immediately terminated and Flash is reset to read mode. When RESET and CE

are held High, the Flash memory is put into standby mode. Do not apply V

ID

to

the RESET pin. The RESET is connected to the System ACE MPM controller

that has a maximum tolerance of 3.6V.

CE

I/O

Flash memory chip enable. When RESET and CE are held High, the Flash

memory is put into standby mode.

OE

I/O

Flash memory output enable.

WE

I/O

Flash memory write enable.

RY/BY

Output

Flash memory ready/busy signal. Open-drain output. When Low, the RD/BY

signal indicates that the Flash is actively erasing, programming, or resetting.

XCCACEM16 and XCCACEM32 only.

WP

I/O

Flash memory hardware write protect.

ACC

Input

Flash memory accelerated mode pin. Do not apply V

HH

to the XCCACEM32

WP/ACC pin. The XCCACEM32 WP/ACC pin is connected to the System ACE

MPM controller that has a maximum tolerance of 3.6V. The XCCACEM64 ACC

pin is independent of the rest of the System ACE MPM and may be used to put

the Flash memory into accelerated program operation.

FLASH_IO_LEVEL

Input

Flash memory V

IO

pin on the XCCACEM64 only. This pin must be connected

to 3.3V for compatibility with the System ACE MPM controller.

BYTE

Input

Flash memory byte-wide data bus mode. XCCACEM16 and XCCACEM32

only. This pin must be connected to 3.3V for compatibility with the System ACE

MPM controller and thus only the 16-bit, word mode is available for accessing

the Flash memory in the system.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCD3558 | GEWINDELOCHBOHRER HEXIBIT M3.5 M5 M8 |

| XCD358 | GEWINDELOCHBOHRER HEXIBIT M3 M5 M8 |

| XCD4610 | GEWINDELOCHBOHRER HEXIBIT M4 M6 M10 |

| XCF5102PV16A | 32-Bit Microprocessor |

| XCF5102PV20A | 32-Bit Microprocessor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCCACE-TQ144 | 制造商:XILINX 制造商全稱:XILINX 功能描述:System ACE CompactFlash Solution |

| XCCACE-TQ144I | 功能描述:IC ACE CONTROLLER CHIP RoHS:否 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| XCCACE-TQG144I | 功能描述:IC ACE CONTROLLER CHIP TQ144 RoHS:是 類別:集成電路 (IC) >> 接口 - 控制器 系列:- 標(biāo)準(zhǔn)包裝:4,900 系列:- 控制器類型:USB 2.0 控制器 接口:串行 電源電壓:3 V ~ 3.6 V 電流 - 電源:135mA 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:36-VFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:36-QFN(6x6) 包裝:* 其它名稱:Q6396337A |

| XCCAE7C13N | 制造商:Schneider Electric 功能描述:ABSOLUTE ENCDER SINGLE TURN 13 BITS 11 30V DC 制造商:SCHNEIDER ELECTRIC 功能描述:ABSOLUTE ENCDER SINGLE TURN |

| XCC-C0 | 制造商:Excelsys Technologies 功能描述:ELECTRONIC PART |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。