- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄225573 > XC7K420T-2FFG901E (XILINX INC) FPGA, PBGA900 PDF資料下載

參數(shù)資料

| 型號: | XC7K420T-2FFG901E |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | FPGA, PBGA900 |

| 封裝: | LEAD FREE, FBGA-900 |

| 文件頁數(shù): | 37/50頁 |

| 文件大小: | 1218K |

| 代理商: | XC7K420T-2FFG901E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

Kintex-7 FPGAs Data Sheet: DC and Switching Characteristics

DS182 (v1.1) April 1, 2011

Advance Product Specification

42

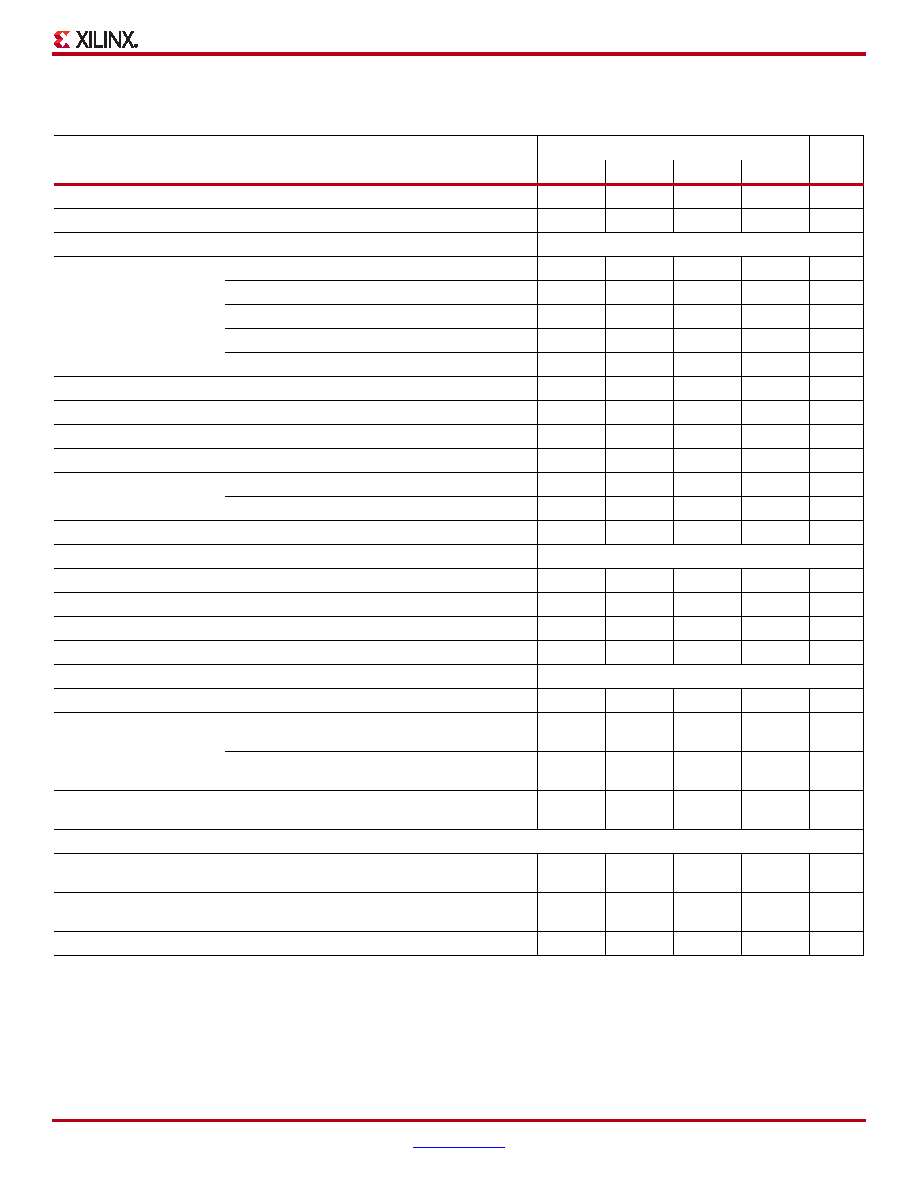

MMCM Switching Characteristics

Table 45: MMCM Specification

Symbol

Description

Speed Grade

Units

-3

-2

-1

-1L

MMCM_FINMAX

Maximum Input Clock Frequency

1066

933

800

MHz

MMCM_FINMIN

Minimum Input Clock Frequency

10

MHz

FINJITTER

Maximum Input Clock Period Jitter

< 20% of clock input period or 1 ns Max

MMCM_FINDUTY

Allowable Input Duty Cycle: 10—49 MHz

25

%

Allowable Input Duty Cycle: 50—199 MHz

30

%

Allowable Input Duty Cycle: 200—399 MHz

35

%

Allowable Input Duty Cycle: 400—499 MHz

40

%

Allowable Input Duty Cycle: >500 MHz

45

%

MMCM_FMIN_PSCLK

Minimum Dynamic Phase Shift Clock Frequency

0.01

MHz

MMCM_FMAX_PSCLK

Maximum Dynamic Phase Shift Clock Frequency

550

500

450

MHz

MMCM_FVCOMIN

Minimum MMCM VCO Frequency

600

MHz

MMCM_FVCOMAX

Maximum MMCM VCO Frequency

1600

1440

1200

MHz

MMCM_FBANDWIDTH

Low MMCM Bandwidth at Typical(1)

1.22

MHz

High MMCM Bandwidth at Typical(1)

4.88

MHz

MMCM_TSTATPHAOFFSET

Static Phase Offset of the MMCM Outputs(2)

0.12

ns

TOUTJITTER

PLL Output Jitter(3)

Note 1

MMCM_TOUTDUTY

MMCM Output Clock Duty Cycle Precision(4)

0.19

0.25

ns

MMCM_TLOCKMAX

MMCM Maximum Lock Time

122

s

MMCM_FOUTMAX

MMCM Maximum Output Frequency

1066

933

800

MHz

MMCM_FOUTMIN

MMCM Minimum Output Frequency(5)(6)

4.69

MHz

TEXTFDVAR

External Clock Feedback Variation

< 20% of clock input period or 1 ns Max

MMCM_RSTMINPULSE

Minimum Reset Pulse Width

5.00

ns

MMCM_FPFDMAX

Maximum Frequency at the Phase Frequency

Detector with Bandwidth Set to High or Optimized

550

500

450

MHz

Maximum Frequency at the Phase Frequency

Detector with Bandwidth Set to Low

550

500

450

MHz

MMCM_FPFDMIN

Minimum Frequency at the Phase Frequency

Detector

10

MHz

MMCM Switching Characteristics Setup and Hold

TMMCMDCK_PSEN/

TMMCMCKD_PSEN

Setup and Hold of Phase Shift Enable

1.04/

0.00

1.04/

0.00

1.04/

0.00

ns

TMMCMDCK_PSINCDEC/

TMMCMCKD_PSINCDEC

Setup and Hold of Phase Shift

Increment/Decrement

1.04/

0.00

1.04/

0.00

1.04/

0.00

ns

TMMCMCKO_PSDONE

Phase Shift Clock-to-Out of PSDONE

0.37

0.40

0.44

ns

Notes:

1.

The MMCM does not filter typical spread-spectrum input clocks because they are usually far below the bandwidth filter frequencies.

2.

The static offset is measured between any MMCM outputs with identical phase.

3.

Values for this parameter are available in the Architecture Wizard.

4.

Includes global clock buffer.

5.

Calculated as FVCO/128 assuming output duty cycle is 50%.

6.

When CASCADE4_OUT = TRUE, FOUTMIN is 0.036 MHz.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC7K420T-2FFG901I | FPGA, PBGA900 |

| XC7K420T-3FFG1156C | FPGA, PBGA1156 |

| XC7K420T-3FFG1156E | FPGA, PBGA1156 |

| XC7K420T-3FFG1156I | FPGA, PBGA1156 |

| XC7K420T-3FFG901C | FPGA, PBGA900 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC7K420T-2FFG901I | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 901FBGA |

| XC7K420T-3FF1156E | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 1156FBGA 制造商:Xilinx 功能描述:IC FPGA 400 I/O 1156FCBGA |

| XC7K420T-3FF901E | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 901FBGA 制造商:Xilinx 功能描述:IC FPGA 380 I/O 901FCBGA |

| XC7K420T-3FFG1156E | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 1156FBGA |

| XC7K420T-3FFG901E | 制造商:Xilinx 功能描述:KINTEX-7 - Trays 制造商:Xilinx 功能描述:IC FPGA 420K KINTEX-7 901FBGA 制造商:Xilinx 功能描述:IC FPGA 380 I/O 901FCBGA |

發(fā)布緊急采購,3分鐘左右您將得到回復。