- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371339 > XC5210-3PC84I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號: | XC5210-3PC84I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 10/73頁 |

| 文件大小: | 598K |

| 代理商: | XC5210-3PC84I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

XC5200 Series Field Programmable Gate Arrays

7-92

November 5, 1998 (Version 5.2)

non-zero hold, attach a NODELAY attribute or property to

the flip-flop or input buffer.

IOB Output Signals

Output signals can be optionally inverted within the IOB,

and pass directly to the pad. As with the inputs, a CLB

flip-flop or latch can be used to store the output signal.

An active-High 3-state signal can be used to place the out-

put buffer in a high-impedance state, implementing 3-state

outputs or bidirectional I/O. Under configuration control,

the output (OUT) and output 3-state (T) signals can be

inverted. The polarity of these signals is independently

configured for each IOB.

The XC5200 devices provide a guaranteed output sink cur-

rent of 8 mA.

Supported destinations for XC5200-Series device outputs

are shown in

Table 6

.(For a detailed discussion of how to

interface between 5 V and 3.3 V devices, see the 3V Prod-

ucts section of The Programmable Logic Data Book)

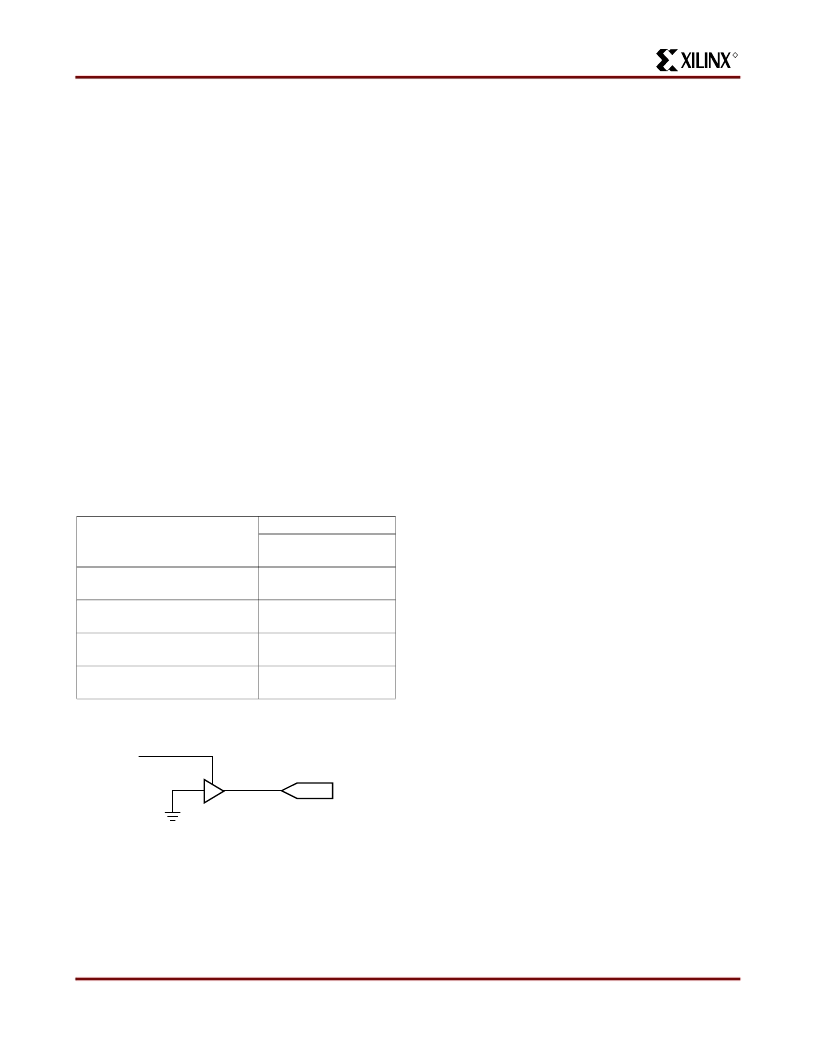

An output can be configured as open-drain (open-collector)

by placing an OBUFT symbol in a schematic or HDL code,

then tying the 3-state pin (T) to the output signal, and the

input pin (I) to Ground. (See

Figure 12

.)

Table 6: Supported Destinations for XC5200-Series

Outputs

Output Slew Rate

The slew rate of each output buffer is, by default, reduced,

to minimize power bus transients when switching non-criti-

cal signals. For critical signals, attach a FAST attribute or

property to the output buffer or flip-flop.

For XC5200 devices, maximum total capacitive load for

simultaneous fast mode switching in the same direction is

200 pF for all package pins between each Power/Ground

pin pair. For some XC5200 devices, additional internal

Power/Ground pin pairs are connected to special Power

and Ground planes within the packages, to reduce ground

bounce.

For slew-rate limited outputs this total is two times larger for

each device type: 400 pF for XC5200 devices. This maxi-

mum capacitive load should not be exceeded, as it can

result in ground bounce of greater than 1.5 V amplitude and

more than 5 ns duration. This level of ground bounce may

cause undesired transient behavior on an output, or in the

internal logic. This restriction is common to all high-speed

digital ICs, and is not particular to Xilinx or the XC5200

Series.

XC5200-Series devices have a feature called “Soft

Start-up,” designed to reduce ground bounce when all out-

puts are turned on simultaneously at the end of configura-

tion. When the configuration process is finished and the

device starts up, the first activation of the outputs is auto-

matically slew-rate limited. Immediately following the initial

activation of the I/O, the slew rate of the individual outputs

is determined by the individual configuration option for

each IOB.

Global Three-State

A separate Global 3-State line (not shown in

Figure 11

)

forces all FPGA outputs to the high-impedance state,

unless boundary scan is enabled and is executing an

EXTEST instruction. This global net (GTS) does not com-

pete with other routing resources; it uses a dedicated distri-

bution network.

GTS can be driven from any user-programmable pin as a

global 3-state input. To use this global net, place an input

pad and input buffer in the schematic or HDL code, driving

the GTS pin of the STARTUP symbol. A specific pin loca-

tion can be assigned to this input using a LOC attribute or

property, just as with any other user-programmable pad. An

inverter can optionally be inserted after the input buffer to

invert the sense of the Global 3-State signal. Using GTS is

similar to Global Reset. See

Figure 8 on page 90

for

details. Alternatively, GTS can be driven from any internal

node.

Other IOB Options

There are a number of other programmable options in the

XC5200-Series IOB.

Pull-up and Pull-down Resistors

Programmable IOB pull-up and pull-down resistors are

useful for tying unused pins to Vcc or Ground to minimize

power consumption and reduce noise sensitivity. The con-

figurable pull-up resistor is a p-channel transistor that pulls

Destination

XC5200 Output Mode

5 V,

CMOS

XC5200 device, V

CC

=3.3 V,

CMOS-threshold inputs

Any typical device, V

CC

= 3.3 V,

CMOS-threshold inputs

Any device, V

CC

= 5 V,

TTL-threshold inputs

Any device, V

CC

= 5 V,

CMOS-threshold inputs

√

some

1

1. Only if destination device has 5-V tolerant inputs

√

√

X6702

OPAD

OBUFT

Figure 12: Open-Drain Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5210-3PG223I | Field Programmable Gate Array (FPGA) |

| XC5210-3PQ160I | Field Programmable Gate Array (FPGA) |

| XC5210-4PG223I | Field Programmable Gate Array (FPGA) |

| XC5210-4PQ160I | Field Programmable Gate Array (FPGA) |

| XC5210-4PQ208I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5210-3PG156C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-3PG191C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-3PG223C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5210-3PG223I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5210-3PG299C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。