- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371341 > XC5204 (Xilinx, Inc.) Field Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門(mén)陣列) PDF資料下載

參數(shù)資料

| 型號(hào): | XC5204 |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Field Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門(mén)陣列) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門(mén)陣列(現(xiàn)場(chǎng)可編程門(mén)陣列) |

| 文件頁(yè)數(shù): | 35/73頁(yè) |

| 文件大?。?/td> | 598K |

| 代理商: | XC5204 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)

R

November 5, 1998 (Version 5.2)

7-117

XC5200 Series Field Programmable Gate Arrays

7

.

Note:

1. At power-up, V

must rise from 2.0 V to V

CC

min in less then 25 ms, otherwise delay configuration by pulling PROGRAM

Low until V

is Valid.

2. The first Data byte is loaded and CCLK starts at the end of the first RCLK active cycle (rising edge).

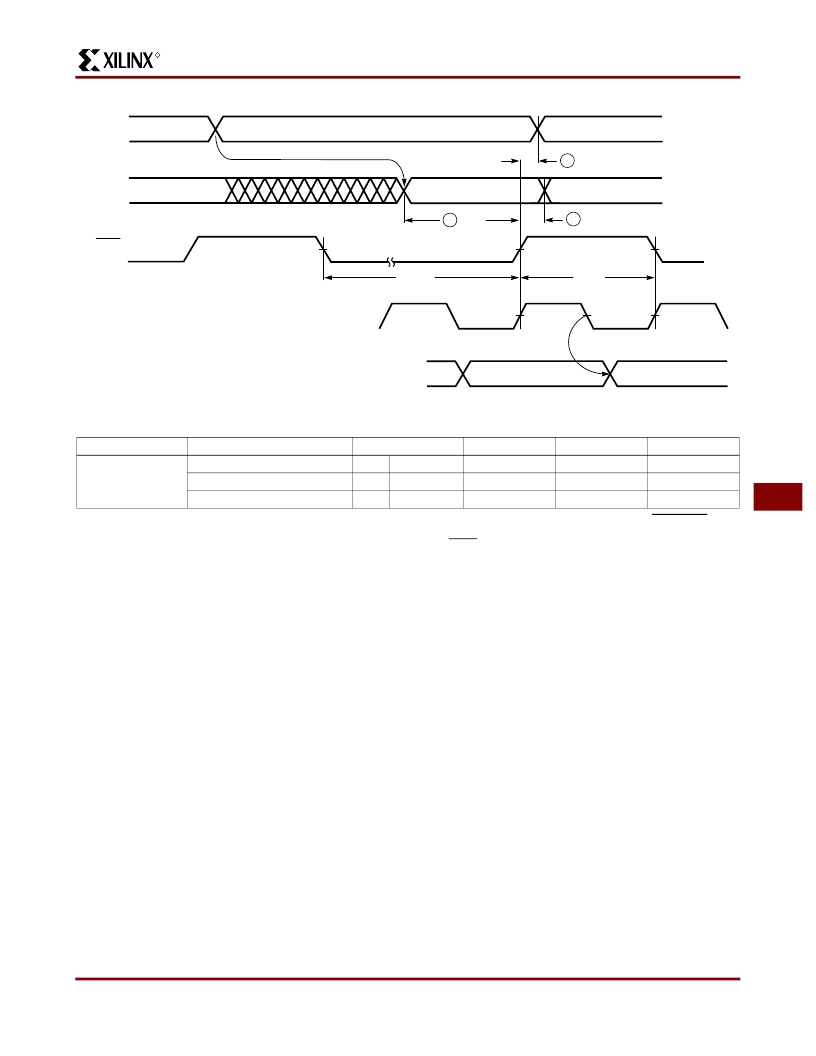

This timing diagram shows that the EPROM requirements are extremely relaxed. EPROM access time can be longer than

500 ns. EPROM data output has no hold-time requirements.

Figure 32: Master Parallel Mode Programming Switching Characteristics

Address for Byte n

Byte

2 T

DRC

Address for Byte n + 1

D7

D6

A0-A17

(output)

D0-D7

RCLK

(output)

CCLK

(output)

DOUT

(output)

1 T

RAC

7 CCLKs

CCLK

3 T

RCD

Byte n - 1

X6078

Description

Symbol

Min

0

60

0

Max

200

Units

ns

ns

ns

CCLK

Delay to Address valid

Data setup time

Data hold time

1

2

3

T

RAC

T

DRC

T

RCD

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5215 | Field Programmable Gate Arrays(現(xiàn)場(chǎng)可編程門(mén)陣列) |

| XC56309GC100 | 24-Bit Digital Signal Processor |

| XC612N2533ML | Analog IC |

| XC612N2533MR | Analog IC |

| XC612N2550ML | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5204-3BG225C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-3BG352C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-3HQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-3HQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-3PC84C | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。