- 您現(xiàn)在的位置:買賣IC網 > PDF目錄371339 > XC5204-5VQ100I Field Programmable Gate Array (FPGA) PDF資料下載

參數資料

| 型號: | XC5204-5VQ100I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數: | 46/73頁 |

| 文件大?。?/td> | 598K |

| 代理商: | XC5204-5VQ100I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁當前第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

XC5200 Series Field Programmable Gate Arrays

7-128

November 5, 1998 (Version 5.2)

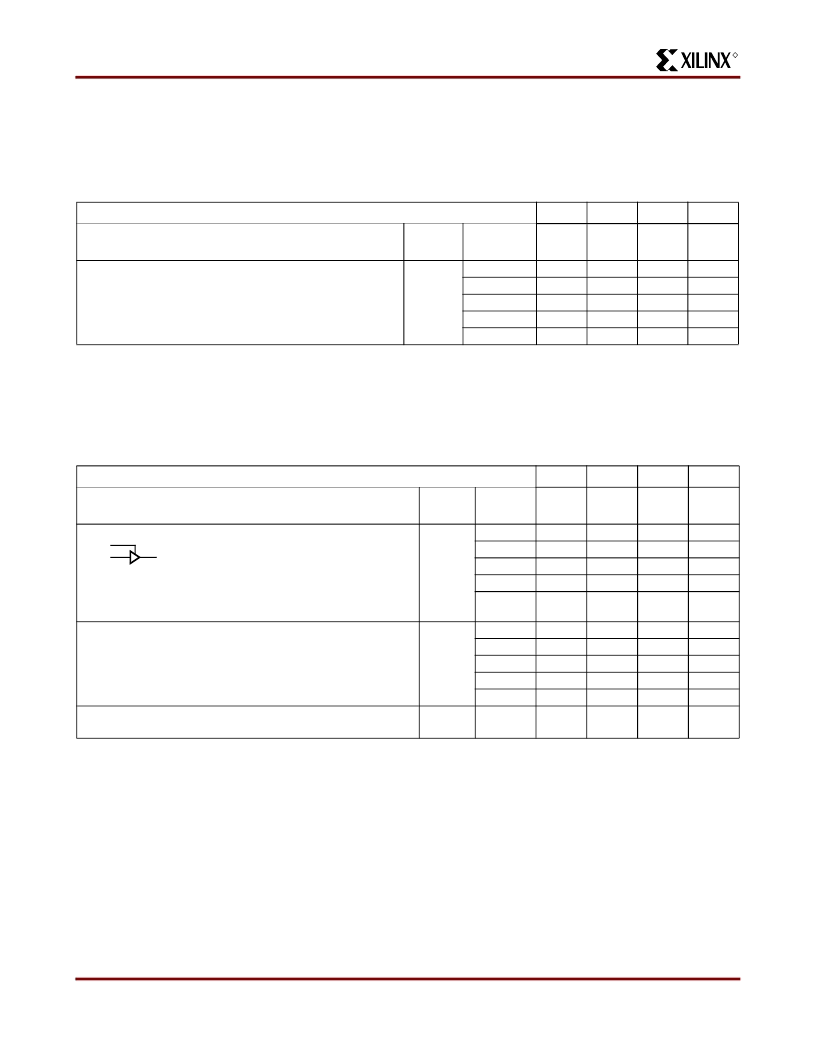

XC5200 Global Buffer Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%

functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark

timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more

detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used

in the simulator.

XC5200 Longline Switching Characteristic Guidelines

Testing of the switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100%

functionally tested. Since many internal timing parameters cannot be measured directly, they are derived from benchmark

timing patterns. The following guidelines reflect worst-case values over the recommended operating conditions. For more

detailed, more precise, and more up-to-date timing information, use the values provided by the timing calculator and used

in the simulator.

Speed Grade

-6

-5

-4

-3

Description

Symbol

Device

Max

(ns)

9.1

9.3

9.4

9.4

10.5

Max

(ns)

8.5

8.7

8.8

8.8

9.9

Max

(ns)

8.0

8.2

8.3

8.5

9.8

Max

(ns)

6.9

7.6

7.7

7.7

9.6

Global Signal Distribution

From pad through global buffer, to any clock (CK)

T

BUFG

XC5202

XC5204

XC5206

XC5210

XC5215

Speed Grade

-6

-5

-4

-3

Description

Symbol

Device

Max

(ns)

6.0

6.4

6.6

6.6

7.3

Max

(ns)

3.8

4.1

4.2

4.2

4.6

Max

(ns)

3.0

3.2

3.3

3.3

3.8

Max

(ns)

2.0

2.3

2.7

2.9

3.2

TBUF driving a Longline

TS

I

TBUF

I to Longline, while TS is Low; i.e., buffer is constantly ac-

tive

TS going Low to Longline going from floating High or Low

to active Low or High

T

IO

XC5202

XC5204

XC5206

XC5210

XC5215

T

ON

XC5202

XC5204

XC5206

XC5210

XC5215

XC52xx

7.8

8.3

8.4

8.4

8.9

3.0

5.6

5.9

6.0

6.0

6.3

2.8

4.7

4.9

5.0

5.0

5.3

2.6

4.0

4.3

4.4

4.4

4.5

2.4

TS going High to TBUF going inactive, not driving

Longline

Note:

1. Die-size-dependent parameters are based upon XC5215 characterization. Production specifications will vary with array

size.

T

OFF

O

相關PDF資料 |

PDF描述 |

|---|---|

| XC5204-6PC84I | Field Programmable Gate Array (FPGA) |

| XC5206-3PC84I | Field Programmable Gate Array (FPGA) |

| XC5206-3PG191I | Field Programmable Gate Array (FPGA) |

| XC5206-3PQ100I | Field Programmable Gate Array (FPGA) |

| XC5206-4PQ100I | Field Programmable Gate Array (FPGA) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XC5204-5VQ64C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-6BG225C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-6BG352C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-6HQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-6HQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。