- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371340 > XC5204-5PC84I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號(hào): | XC5204-5PC84I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場(chǎng)可編程門陣列(FPGA) |

| 文件頁數(shù): | 19/73頁 |

| 文件大小: | 598K |

| 代理商: | XC5204-5PC84I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當(dāng)前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

R

November 5, 1998 (Version 5.2)

7-101

XC5200 Series Field Programmable Gate Arrays

7

Even if the boundary scan symbol is used in a schematic,

the input pins TMS, TCK, and TDI can still be used as

inputs to be routed to internal logic. Care must be taken not

to force the chip into an undesired boundary scan state by

inadvertently applying boundary scan input patterns to

these pins. The simplest way to prevent this is to keep

TMS High, and then apply whatever signal is desired to TDI

and TCK.

Avoiding Inadvertent Boundary Scan

If TMS or TCK is used as user I/O, care must be taken to

ensure that at least one of these pins is held constant dur-

ing configuration. In some applications, a situation may

occur where TMS or TCK is driven during configuration.

This may cause the device to go into boundary scan mode

and disrupt the configuration process.

To prevent activation of boundary scan during configura-

tion, do either of the following:

TMS: Tie High to put the Test Access Port controller

in a benign RESET state

TCK: Tie High or Low—do not toggle this clock input.

For more information regarding boundary scan, refer to the

Xilinx Application Note XAPP 017, “

Boundary Scan in

XC4000 and XC5200 Devices

.“

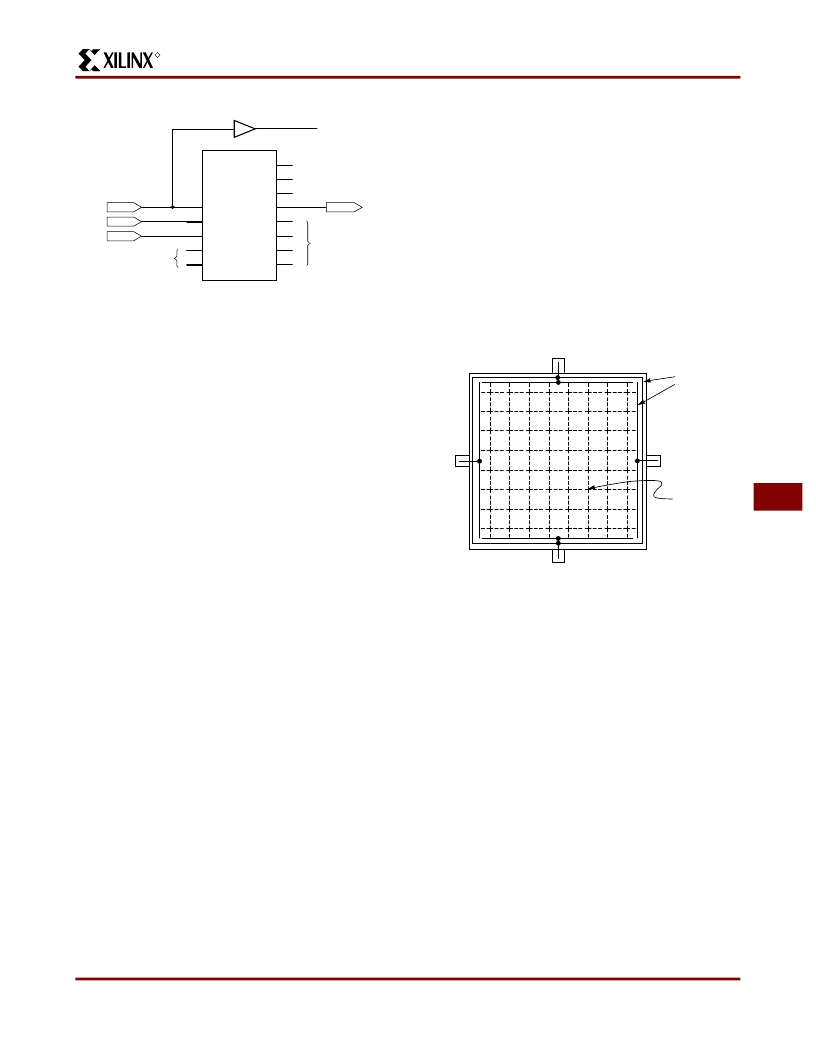

Power Distribution

Power for the FPGA is distributed through a grid to achieve

high noise immunity and isolation between logic and I/O.

Inside the FPGA, a dedicated Vcc and Ground ring sur-

rounding the logic array provides power to the I/O drivers,

as shown in

Figure 21

. An independent matrix of Vcc and

Ground lines supplies the interior logic of the device.

This power distribution grid provides a stable supply and

ground for all internal logic, providing the external package

power pins are all connected and appropriately decoupled.

Typically, a 0.1

μ

F capacitor connected near the Vcc and

Ground pins of the package will provide adequate decou-

pling.

Output buffers capable of driving/sinking the specified 8 mA

loads under specified worst-case conditions may be capa-

ble of driving/sinking up to 10 times as much current under

best case conditions.

Noise can be reduced by minimizing external load capaci-

tance and reducing simultaneous output transitions in the

same direction. It may also be beneficial to locate heavily

loaded output buffers near the Ground pads. The I/O Block

output buffers have a slew-rate limited mode (default)

which should be used where output rise and fall times are

not speed-critical.

Pin Descriptions

There are three types of pins in the XC5200-Series

devices:

Permanently dedicated pins

User I/O pins that can have special functions

Unrestricted user-programmable I/O pins.

Before and during configuration, all outputs not used for the

configuration process are 3-stated and pulled high with a

20 k

- 100 k

pull-up resistor.

After configuration, if an IOB is unused it is configured as

an input with a 20 k

- 100 k

pull-up resistor.

Device pins for XC5200-Series devices are described in

Table 9

. Pin functions during configuration for each of the

seven configuration modes are summarized in

“Pin Func-

TDI

TMS

TCK

TDO1

TDO2

TDO

DRCK

IDLE

SEL1

SEL2

RESET

UPDATE

SHIFT

BSCAN

To User

Logic

IBUF

Optional

From

User Logic

To User

Logic

X9000

Figure 20: Boundary Scan Schematic Example

GND

Ground and

Vcc Ring for

I/O Drivers

Vcc

GND

Vcc

Logic

Power Grid

X5422

Figure 21: XC5200-Series Power Distribution

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC5204-5PG156I | Field Programmable Gate Array (FPGA) |

| XC5204-5PQ100I | Field Programmable Gate Array (FPGA) |

| XC5204-5PQ160I | Field Programmable Gate Array (FPGA) |

| XC5204-5TQ144I | Field Programmable Gate Array (FPGA) |

| XC5204-6PQ100I | Field Programmable Gate Array (FPGA) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC5204-5PG156C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-5PG156I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5204-5PG191C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-5PG223C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5204-5PG299C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。