- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374999 > XC4044XLA-08HQ240I (XILINX INC) XC4000XLA/XV Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號: | XC4044XLA-08HQ240I |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | XC4000XLA/XV Field Programmable Gate Arrays |

| 中文描述: | FPGA, 1600 CLBS, 27000 GATES, 263 MHz, PQFP240 |

| 封裝: | QFP-240 |

| 文件頁數(shù): | 8/14頁 |

| 文件大小: | 142K |

| 代理商: | XC4044XLA-08HQ240I |

R

XC4000XLA/XV Field Programmable Gate Arrays

6-164

DS015 (v1.3) October 18, 1999 - Product Specification

clocked in on each consecutive rising CCLK edge

(

Figure 6

).

Pseudo Daisy Chain

As illustrated in Figures 5 and 6, multiple devices with dif-

ferent configurations can be configured in a pseudo daisy

chain provided that all of the devices are in Express mode.

A single combined byte-wide data stream is used to config-

ure the chain of Express mode devices. CCLK pins are tied

together and D0-D7 pins are tied together as a data buss

for all devices along the chain. A status signal is passed

from DOUT of each device to the CS1 input of the device

which follows it in the chain. Frame data is accepted only

when CS1 is High and the device’s configuration memory is

not already full. The lead device in the chain has its CS1

input tied High (or floating, since there is an internal pullup).

The status pin DOUT is initially High for all devices in the

chain until the data stream header of seven bytes is loaded.

This allows header data to be loaded into all devices in the

chain simultaneously. After the header is loaded in all

devices, their DOUT pins are pulled Low disabling configu-

ration of all devices in the chain except the first device. As

each device in the chain is filled, its DOUT goes High driv-

ing High the CS1 input of the next device, thereby enabling

configuration of the next device in the pseudo daisy chain.

The requirement that all DONE pins in a daisy chain be

wired together applies only to Express mode, and only if all

devices in the chain are to become active simultaneously.

All 4000XLA/XV devices in Express mode are synchro-

nized to the DONE pin. User I/O for each device becomes

active after the DONE pin for that device goes High (The

exact timing is determined by BitGen options.)

Since the DONE pin is open-drain and does not drive a

High value, tying the DONE pins of all devices together pre-

vents all devices in the chain from going High until the last

device in the chain has completed its configuration cycle. If

the DONE pin of a device is left unconnected, the device

becomes active as soon as that device has been config-

ured.

Because only XC4000XLA/XV, SpartanXL, and XC5200

devices support Express mode, only these devices can be

used to form an Express mode pseudo daisy chain.

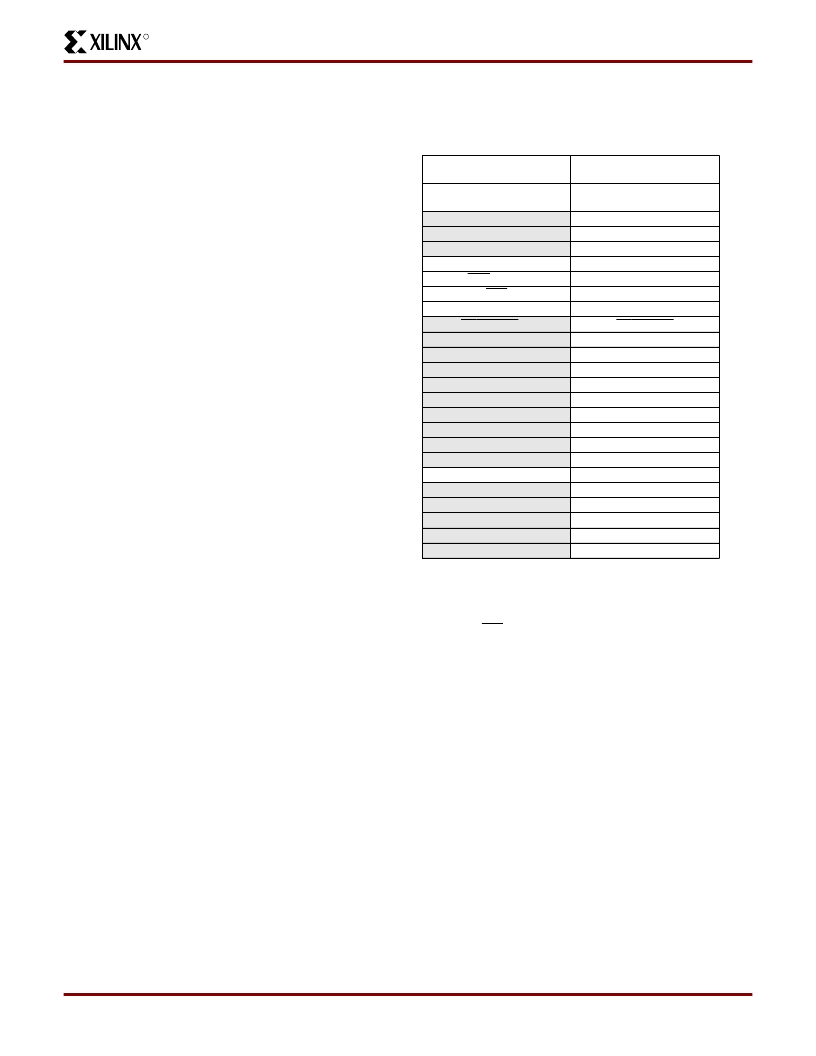

Table 7: Pin Functions During Configuration

(4000XLA/XV Express mode only)

CONFIGURATION MODE

<M2:M1:M0>

EXPRESS MODE

<0:1:0>

M2(LOW) (I)

M1(HIGH) (I)

M0(LOW) (I)

HDC (HIGH)

LDC (LOW)

INIT

DONE

PROGRAM (I)

CCLK (I)

DATA 7 (I)

DATA 6 (I)

DATA 5 (I)

DATA 4 (I)

DATA 3 (I)

DATA 2 (I)

DATA 1 (I)

DATA 0 (I)

DOUT

TDI

TCK

TMS

TDO

CS1

Notes

1. A shaded table cell represents the internal

pull-up used before and during

configuration.

2. (I) represents an input; (O) represents an

output.

3. INIT is an open-drain output during

configuration.

USER

OPERATION

PIN FUNCTION

M2

M1

M0

I/O

I/O

I/O

DONE

CCLK (I)

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

SGCK4-I/O

TDI-I/O

TCK-I/O

TMS-I/O

TDO-(O)

I/O

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4044XL | XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4044XLA | XC4000XLA/XV Field Programmable Gate Arrays |

| XC40250XV | XC4000XLA/XV Field Programmable Gate Arrays |

| XC40150XV | XC4000XLA/XV Field Programmable Gate Arrays |

| XC40110XV | XC4000XLA/XV Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4044XLA09BG352C | 制造商:Xilinx 功能描述: |

| XC4044XLA-09BG352C | 制造商:Xilinx 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| XC4044XLA-09BG352I | 制造商:Xilinx 功能描述: 制造商: 功能描述: 制造商:undefined 功能描述: |

| XC4044XLA-09BG432C | 制造商:Xilinx 功能描述: |

| XC4044XLA-09HQ160C | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。