- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄4175 > XC4013E-1PQ208C (Xilinx Inc)IC FPGA 576 CLB'S 208-PQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC4013E-1PQ208C |

| 廠商: | Xilinx Inc |

| 文件頁(yè)數(shù): | 35/68頁(yè) |

| 文件大小: | 0K |

| 描述: | IC FPGA 576 CLB'S 208-PQFP |

| 產(chǎn)品變化通告: | Product Discontinuation 28/Jul/2010 |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | XC4000E/X |

| LAB/CLB數(shù): | 576 |

| 邏輯元件/單元數(shù): | 1368 |

| RAM 位總計(jì): | 18432 |

| 輸入/輸出數(shù): | 160 |

| 門(mén)數(shù): | 13000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應(yīng)商設(shè)備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1110 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)當(dāng)前第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)

R

XC4000E and XC4000X Series Field Programmable Gate Arrays

6-44

May 14, 1999 (Version 1.6)

Instruction Set

The XC4000 Series boundary scan instruction set also

includes instructions to congure the device and read back

the conguration data. The instruction set is coded as

shown in Table 17.

Bit Sequence

The bit sequence within each IOB is: In, Out, 3-State. The

input-only M0 and M2 mode pins contribute only the In bit

to the boundary scan I/O data register, while the out-

put-only M1 pin contributes all three bits.

The rst two bits in the I/O data register are TDO.T and

TDO.O, which can be used for the capture of internal sig-

nals. The nal bit is BSCANT.UPD, which can be used to

drive an internal net. These locations are primarily used by

Xilinx for internal testing.

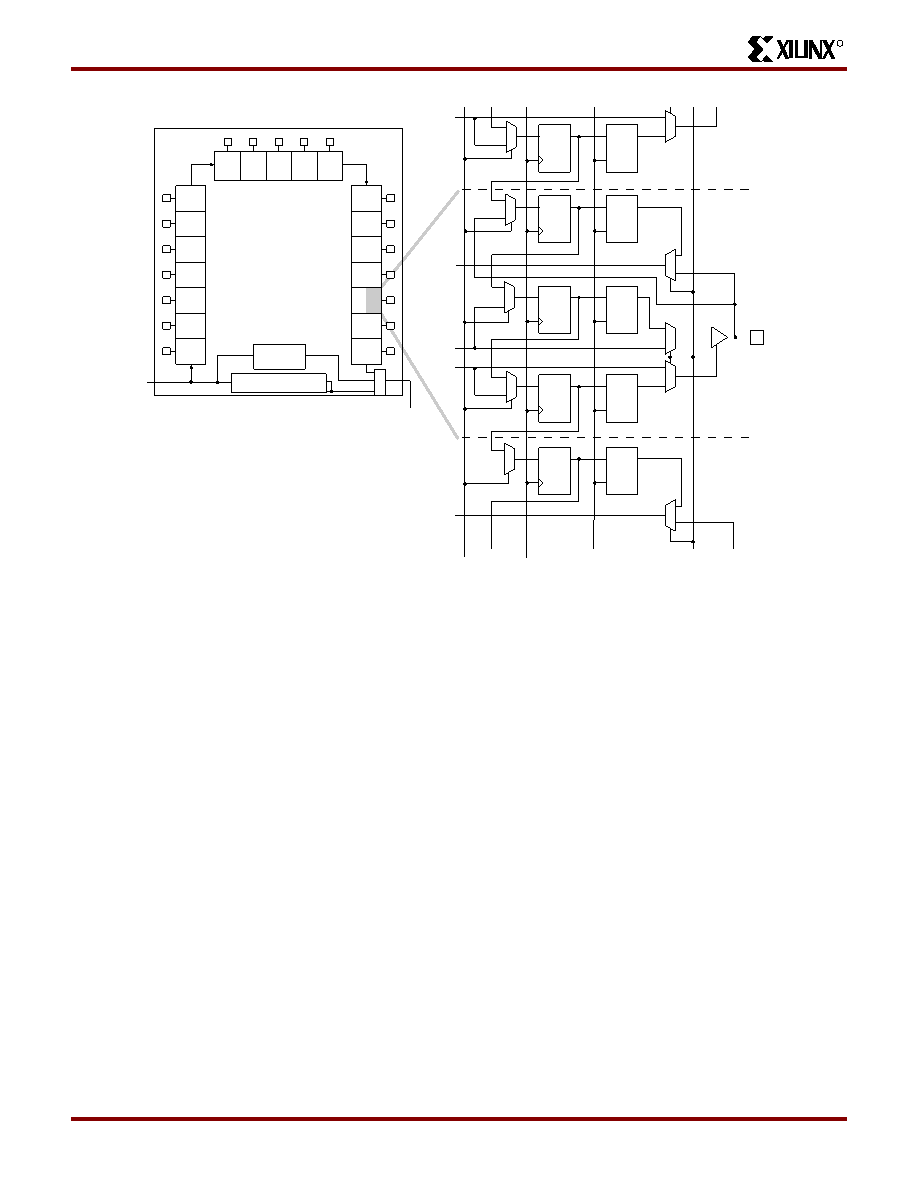

From a cavity-up view of the chip (as shown in XDE or

Epic), starting in the upper right chip corner, the boundary

scan data-register bits are ordered as shown in Figure 42.

The device-specic pinout tables for the XC4000 Series

include the boundary scan locations for each IOB pin.

BSDL (Boundary Scan Description Language) les for

XC4000 Series devices are available on the Xilinx FTP site.

Including Boundary Scan in a Schematic

If boundary scan is only to be used during conguration, no

special schematic elements need be included in the sche-

matic or HDL code. In this case, the special boundary scan

pins TDI, TMS, TCK and TDO can be used for user func-

tions after conguration.

To indicate that boundary scan remain enabled after cong-

uration, place the BSCAN library symbol and connect the

TDI, TMS, TCK and TDO pad symbols to the appropriate

pins, as shown in Figure 43.

Even if the boundary scan symbol is used in a schematic,

the input pins TMS, TCK, and TDI can still be used as

inputs to be routed to internal logic. Care must be taken not

to force the chip into an undesired boundary scan state by

inadvertently applying boundary scan input patterns to

these pins. The simplest way to prevent this is to keep TMS

High, and then apply whatever signal is desired to TDI and

TCK.

D

Q

D

Q

IOB

M

U

X

BYPASS

REGISTER

IOB

TDO

TDI

IOB

1

0

1

0

1

0

1

0

1

0

sd

LE

DQ

D

Q

D

Q

1

0

1

0

1

0

1

0

DQ

LE

sd

LE

DQ

sd

LE

DQ

IOB

D

Q

1

0

DQ

LE

sd

IOB.T

DATA IN

IOB.I

IOB.Q

IOB.T

IOB.I

SHIFT/

CAPTURE

CLOCK DATA

REGISTER

DATAOUT

UPDATE

EXTEST

X9016

INSTRUCTION REGISTER

Figure 41: XC4000 Series Boundary Scan Logic

Product Obsolete or Under Obsolescence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC4013E-4PQ160C | IC FPGA 576 CLB'S 160-PQFP |

| ASC44DRAN-S734 | CONN EDGECARD 88POS .100 R/A PCB |

| ASC44DRAH-S734 | CONN EDGECARD 88POS .100 R/A PCB |

| IDT71V3577S80PFG | IC SRAM 4MBIT 80NS 100TQFP |

| AMM28DSAI | CONN EDGECARD 56POS R/A .156 SLD |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC4013E-1PQ208I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC4013E-1PQ240C | 功能描述:IC FPGA C-TEMP 5V 1SPD 240-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門(mén)陣列) 系列:XC4000E/X 標(biāo)準(zhǔn)包裝:1 系列:Kintex-7 LAB/CLB數(shù):25475 邏輯元件/單元數(shù):326080 RAM 位總計(jì):16404480 輸入/輸出數(shù):350 門(mén)數(shù):- 電源電壓:0.97 V ~ 1.03 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:900-BBGA,F(xiàn)CBGA 供應(yīng)商設(shè)備封裝:900-FCBGA(31x31) 其它名稱:122-1789 |

| XC4013E-1PQ240I | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1PQ240M | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

| XC4013E-1TQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC4000E and XC4000X Series Field Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。