- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄4277 > XC3S500E-4FGG320I (Xilinx Inc)IC FPGA SPARTAN-3E 500K 320-FBGA PDF資料下載

參數(shù)資料

| 型號: | XC3S500E-4FGG320I |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 40/227頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA SPARTAN-3E 500K 320-FBGA |

| 標(biāo)準(zhǔn)包裝: | 84 |

| 系列: | Spartan®-3E |

| LAB/CLB數(shù): | 1164 |

| 邏輯元件/單元數(shù): | 10476 |

| RAM 位總計: | 368640 |

| 輸入/輸出數(shù): | 232 |

| 門數(shù): | 500000 |

| 電源電壓: | 1.14 V ~ 1.26 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | -40°C ~ 100°C |

| 封裝/外殼: | 320-BGA |

| 供應(yīng)商設(shè)備封裝: | 320-FBGA(19x19) |

| 配用: | 122-1536-ND - KIT STARTER SPARTAN-3E |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁當(dāng)前第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁第177頁第178頁第179頁第180頁第181頁第182頁第183頁第184頁第185頁第186頁第187頁第188頁第189頁第190頁第191頁第192頁第193頁第194頁第195頁第196頁第197頁第198頁第199頁第200頁第201頁第202頁第203頁第204頁第205頁第206頁第207頁第208頁第209頁第210頁第211頁第212頁第213頁第214頁第215頁第216頁第217頁第218頁第219頁第220頁第221頁第222頁第223頁第224頁第225頁第226頁第227頁

Spartan-3E FPGA Family: DC and Switching Characteristics

DS312 (v4.1) July 19, 2013

Product Specification

134

Simultaneously Switching Output Guidelines

This section provides guidelines for the recommended

maximum allowable number of Simultaneous Switching

Outputs (SSOs). These guidelines describe the maximum

number of user I/O pins of a given output signal standard

that should simultaneously switch in the same direction,

while maintaining a safe level of switching noise. Meeting

these guidelines for the stated test conditions ensures that

the FPGA operates free from the adverse effects of ground

and power bounce.

Ground or power bounce occurs when a large number of

outputs simultaneously switch in the same direction. The

output drive transistors all conduct current to a common

voltage rail. Low-to-High transitions conduct to the VCCO

rail; High-to-Low transitions conduct to the GND rail. The

resulting cumulative current transient induces a voltage

difference across the inductance that exists between the die

pad and the power supply or ground return. The inductance

is associated with bonding wires, the package lead frame,

and any other signal routing inside the package. Other

variables contribute to SSO noise levels, including stray

inductance on the PCB as well as capacitive loading at

receivers. Any SSO-induced voltage consequently affects

internal switching noise margins and ultimately signal

quality.

guidelines. For each device/package combination, Table 96

provides the number of equivalent VCCO/GND pairs. The

equivalent number of pairs is based on characterization and

might not match the physical number of pairs. For each

output signal standard and drive strength, Table 97

recommends the maximum number of SSOs, switching in

the same direction, allowed per VCCO/GND pair within an

I/O bank. The guidelines in Table 97 are categorized by

package style. Multiply the appropriate numbers from

SSOs allowed within an I/O bank. Exceeding these SSO

guidelines might result in increased power or ground

bounce, degraded signal integrity, or increased system jitter.

The recommended maximum SSO values assumes that the

FPGA is soldered on the printed circuit board and that the

board uses sound design practices. The SSO values do not

apply for FPGAs mounted in sockets, due to the lead

inductance introduced by the socket.

The number of SSOs allowed for quad-flat packages (VQ,

TQ, PQ) is lower than for ball grid array packages (FG) due

to the larger lead inductance of the quad-flat packages. The

results for chip-scale packaging (CP132) are better than

quad-flat packaging but not as high as for ball grid array

packaging. Ball grid array packages are recommended for

applications with a large number of simultaneously

switching outputs.

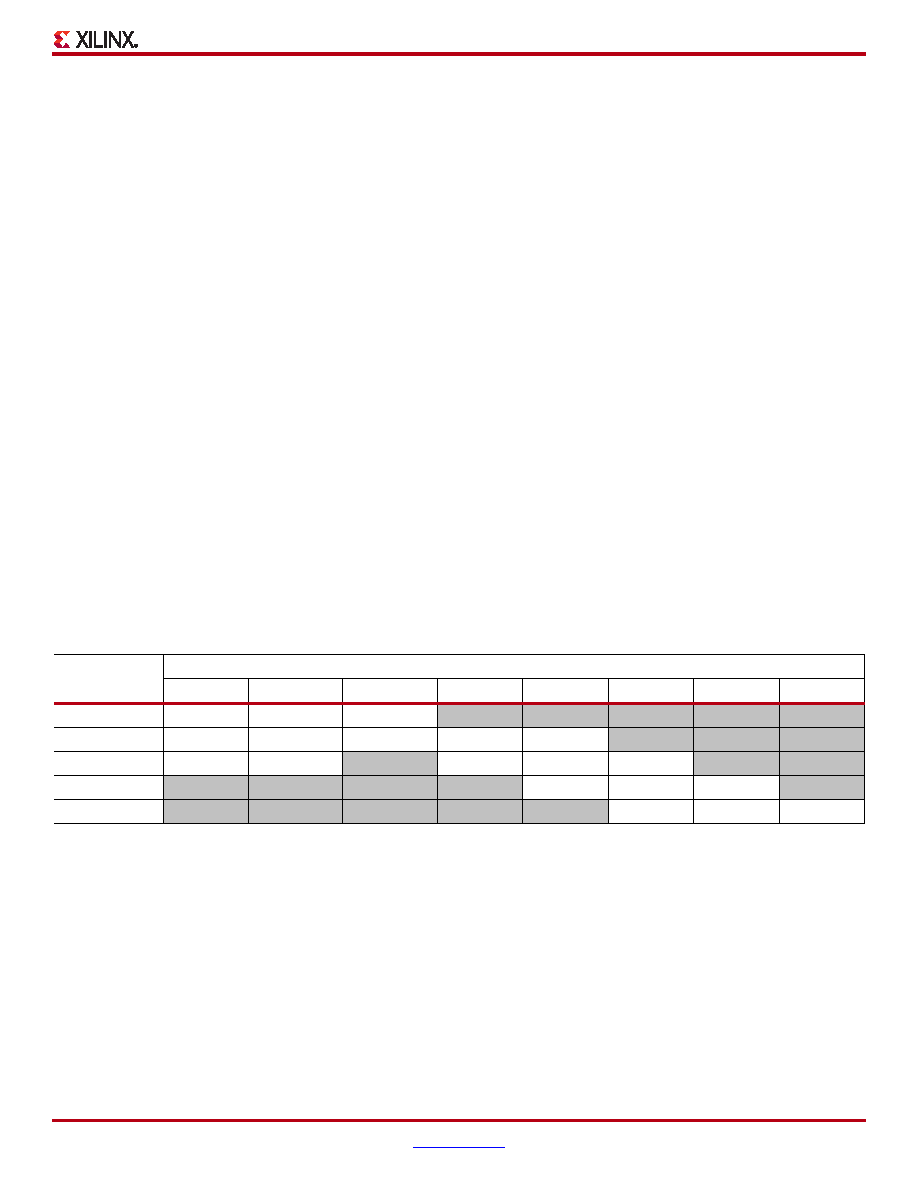

Table 96: Equivalent VCCO/GND Pairs per Bank

Device

Package Style (including Pb-free)

VQ100

CP132

TQ144

PQ208

FT256

FG320

FG400

FG484

XC3S100E

2

-

XC3S250E

2

3

4

-

XC3S500E

2

-

345

-

XC3S1200E

-

4

5

6

-

XC3S1600E

-

-5

6

7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC6SLX25-N3CSG324C | IC FPGA SPARTAN-6 324CSBGA |

| 93LC86CT-I/MNY | IC EEPROM SER 16K 2.5V 8TDFN |

| XC6SLX25-N3FTG256I | IC FPGA SPARTAN-6 256FBGA |

| XC6SLX25-2FT256I | IC FPGA SPARTAN 6 256FTGBGA |

| XC6SLX25-L1FTG256C | IC FPGA SPARTAN 6 24K 256FTGBGA |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3S500E-4FT256C | 制造商:Xilinx 功能描述:FPGA SPARTAN-3E 500K GATES 10476 CELLS 572MHZ 90NM 1.2V 256F - Trays |

| XC3S500E-4FT256I | 功能描述:IC FPGA SPARTAN 3E 256FTBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC3S500E-4FT256I4003 | 制造商:Xilinx 功能描述: |

| XC3S500E-4FTG256C | 功能描述:IC SPARTAN-3E FPGA 500K 256-FTBG RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-3E 標(biāo)準(zhǔn)包裝:60 系列:XP LAB/CLB數(shù):- 邏輯元件/單元數(shù):10000 RAM 位總計:221184 輸入/輸出數(shù):244 門數(shù):- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應(yīng)商設(shè)備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

| XC3S500E-4FTG256C4124 | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。