- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19312 > XC2S50E-6PQG208C (Xilinx Inc)IC SPARTAN-IIE FPGA 50K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | XC2S50E-6PQG208C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 30/108頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-IIE FPGA 50K 208-PQFP |

| 產(chǎn)品變化通告: | FPGA Family Discontinuation 18/Apr/2011 |

| 標準包裝: | 24 |

| 系列: | Spartan®-IIE |

| LAB/CLB數(shù): | 384 |

| 邏輯元件/單元數(shù): | 1728 |

| RAM 位總計: | 32768 |

| 輸入/輸出數(shù): | 146 |

| 門數(shù): | 50000 |

| 電源電壓: | 1.71 V ~ 1.89 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

| 其它名稱: | 122-1330 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁當前第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁

28

DS077-2 (v3.0) August 9, 2013

Product Specification

Spartan-IIE FPGA Family: Functional Description

R

— OBSOLETE — OBSOLETE — OBSOLETE — OBSOLETE —

If CCLK is slower than FCCNH, the FPGA will never assert

BUSY. In this case, the above handshake is unnecessary,

and data can simply be entered into the FPGA every CCLK

cycle.

A configuration packet does not have to be written in one

continuous stretch, rather it can be split into many write

sequences. Each sequence would involve assertion of CS.

In applications where multiple clock cycles may be required

to access the configuration data before each byte can be

loaded into the Slave Parallel interface, a new byte of data

may not be ready for each consecutive CCLK edge. In such

a case the CS signal may be deasserted until the next byte

is valid on D0-D7. While CS is High, the Slave Parallel inter-

face does not expect any data and ignores all CCLK transi-

tions. However, to avoid aborting configuration, WRITE

must continue to be asserted while CS is asserted during

CCLK transitions.

Abort

To abort configuration during a write sequence, deassert

WRITE while holding CS Low. The abort operation is initi-

ated at the rising edge of CCLK. The device will remain

BUSY until the aborted operation is complete. After aborting

configuration, data is assumed to be unaligned to word

boundaries and the FPGA requires a new synchronization

word prior to accepting any new packets.

Boundary-Scan Configuration Mode

In the boundary-scan mode, no nondedicated pins are

required, configuration being done entirely through the

IEEE 1149.1 Test Access Port (TAP).

Configuration through the TAP uses the special CFG_IN

instruction. This instruction allows data input on TDI to be

converted into data packets for the internal configuration

bus.

The following steps are required to configure the FPGA

through the boundary-scan port.

1.

Load the CFG_IN instruction into the boundary-scan

instruction register (IR)

2.

Enter the Shift-DR (SDR) state

3.

Shift a standard configuration bitstream into TDI

4.

Return to Run-Test-Idle (RTI)

5.

Load the JSTART instruction into IR

6.

Enter the SDR state

7.

Clock TCK (if selected) through the startup sequence

(the length is programmable)

8.

Return to RTI

Configuration and readback via the TAP is always available.

The boundary-scan mode simply locks out the other modes.

The boundary-scan mode is selected by a <10x> on the

mode pins (M0, M1, M2). Note that the PROGRAM pin must

be pulled High prior to reconfiguration. A Low on the PRO-

GRAM pin resets the TAP controller and no boundary scan

operations can be performed. See Xilinx Application Note

XAPP188 for more information on boundary-scan configu-

ration.

Readback

The configuration data stored in the Spartan-IIE FPGA con-

figuration memory can be read back for verification. Along

with the configuration data it is possible to read back the

contents of all flip-flops/latches, LUT RAMs, and block

RAMs. This capability is used for real-time debugging.

For more detailed information see Xilinx Application Note

XAPP176, Configuration and Readback of the Spartan-II

and Spartan-IIE FPGA Families.

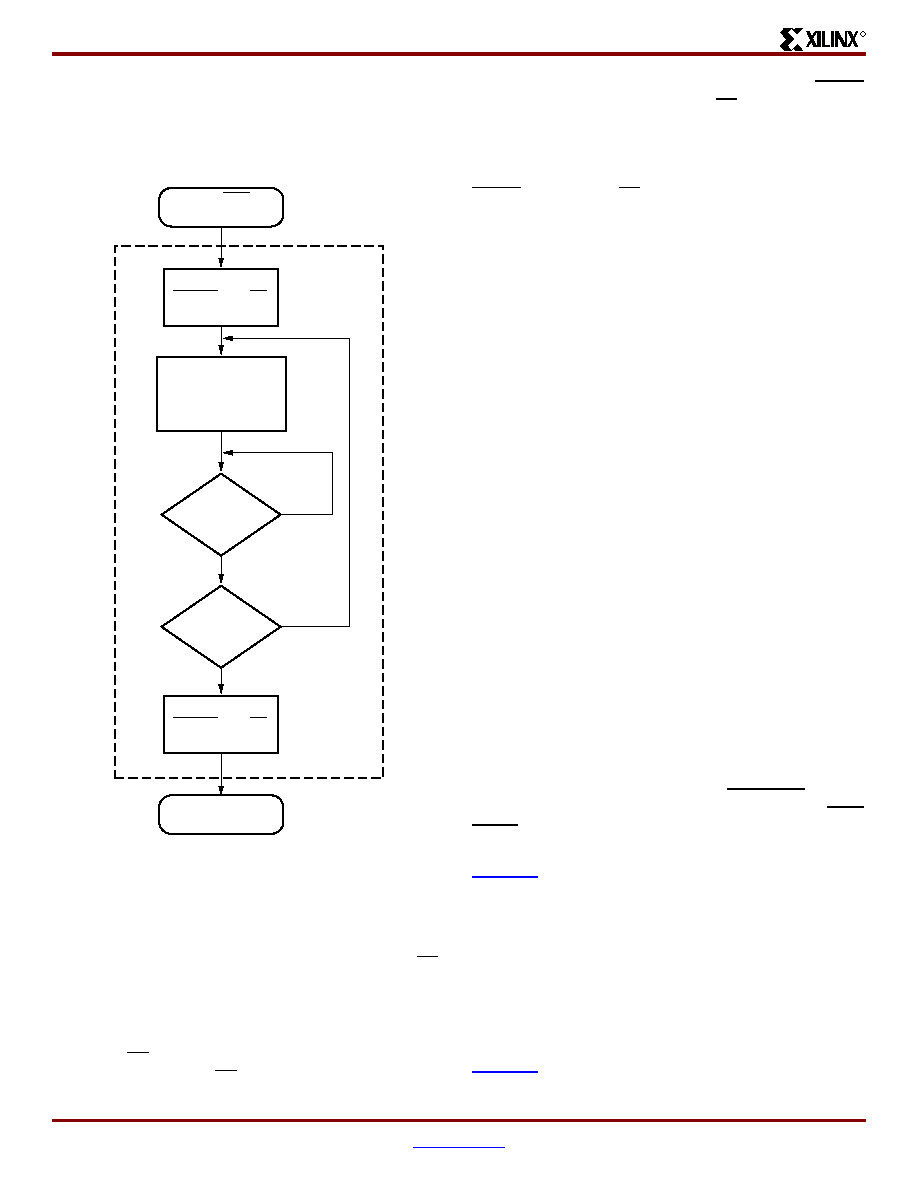

Figure 21: Loading Configuration Data for the Slave

Parallel Mode

Yes

No

FPGA

Driving BUSY

High?

After INIT

Goes High

Load One

Configuration

Byte on Next

CCLK Rising Edge

To CRC Check

DS001_19_032300

No

End of

Configuration

Data File?

Yes

User Drives

WRITE and CS

Low

User Drives

WRITE and CS

High

相關PDF資料 |

PDF描述 |

|---|---|

| AIMC-0805-R12J-T | INDUCTOR MULTILAYER 120NH 0805 |

| XC3S200-4VQG100I | SPARTAN-3 FPGA 200K STD 100VQFP |

| XC3S200A-4VQG100I | IC FPGA SPARTAN-3A 200K 100-VQFP |

| GBM10DCSN | CONN EDGECARD 20POS DIP .156 SLD |

| GBM10DCSH | CONN EDGECARD 20POS DIP .156 SLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S50E-6PQG208I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S50E-6TQ144C | 功能描述:IC FPGA 1.8V 384 CLB'S 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S50E-6TQ144I | 制造商:Xilinx 功能描述:IC SYSTEM GATE |

| XC2S50E-6TQ144Q | 制造商:Rochester Electronics LLC 功能描述: 制造商:Xilinx 功能描述: |

| XC2S50E-6TQG144C | 功能描述:IC SPARTAN-IIE FPGA 50K 144-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Spartan®-IIE 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計:2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

發(fā)布緊急采購,3分鐘左右您將得到回復。