- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄21991 > XC2S30-5VQG100C (Xilinx Inc)IC FPGA 2.5V 216 CLB'S 100-VQFP PDF資料下載

參數(shù)資料

| 型號(hào): | XC2S30-5VQG100C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 31/99頁 |

| 文件大?。?/td> | 0K |

| 描述: | IC FPGA 2.5V 216 CLB'S 100-VQFP |

| 標(biāo)準(zhǔn)包裝: | 90 |

| 系列: | Spartan®-II |

| LAB/CLB數(shù): | 216 |

| 邏輯元件/單元數(shù): | 972 |

| RAM 位總計(jì): | 24576 |

| 輸入/輸出數(shù): | 60 |

| 門數(shù): | 30000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-VQFP(14x14) |

| 產(chǎn)品目錄頁面: | 599 (CN2011-ZH PDF) |

| 其它名稱: | 122-1513-5 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當(dāng)前第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

37

R

support of a wide variety of applications, from general

purpose standard applications to high-speed low-voltage

memory busses.

Versatile I/O blocks also provide selectable output drive

strengths and programmable slew rates for the LVTTL

output buffers, as well as an optional, programmable weak

pull-up, weak pull-down, or weak "keeper" circuit ideal for

use in external bussing applications.

Each Input/Output Block (IOB) includes three registers, one

each for the input, output, and 3-state signals within the

IOB. These registers are optionally configurable as either a

D-type flip-flop or as a level sensitive latch.

The input buffer has an optional delay element used to

guarantee a zero hold time requirement for input signals

registered within the IOB.

The Versatile I/O features also provide dedicated resources

for input reference voltage (VREF) and output source

voltage (VCCO), along with a convenient banking system

that simplifies board design.

By taking advantage of the built-in features and wide variety

of I/O standards supported by the Versatile I/O features,

system-level design and board design can be greatly

simplified and improved.

Fundamentals

Modern bus applications, pioneered by the largest and most

influential companies in the digital electronics industry, are

commonly introduced with a new I/O standard tailored

specifically to the needs of that application. The bus I/O

standards provide specifications to other vendors who

create products designed to interface with these

applications. Each standard often has its own specifications

for current, voltage, I/O buffering, and termination

techniques.

The ability to provide the flexibility and time-to-market

advantages of programmable logic is increasingly

dependent on the capability of the programmable logic

device to support an ever increasing variety of I/O

standards

The Versatile I/O resources feature highly configurable

input and output buffers which provide support for a wide

variety of I/O standards. As shown in Table 15, each buffer

type can support a variety of voltage requirements.

Overview of Supported I/O Standards

This section provides a brief overview of the I/O standards

supported by all Spartan-II devices.

While most I/O standards specify a range of allowed

voltages, this document records typical voltage values only.

Detailed information on each specification may be found on

the Electronic Industry Alliance JEDEC website at

. For more details on the I/O standards

and termination application examples, see XAPP179, "Using

SelectIO Interfaces in Spartan-II and Spartan-IIE FPGAs."

LVTTL — Low-Voltage TTL

The Low-Voltage TTL (LVTTL) standard is a general

purpose EIA/JESDSA standard for 3.3V applications that

uses an LVTTL input buffer and a Push-Pull output buffer.

This standard requires a 3.3V output source voltage

(VCCO), but does not require the use of a reference voltage

(VREF) or a termination voltage (VTT).

LVCMOS2 — Low-Voltage CMOS for 2.5V

The Low-Voltage CMOS for 2.5V or lower (LVCMOS2)

standard is an extension of the LVCMOS standard (JESD

8.5) used for general purpose 2.5V applications. This

standard requires a 2.5V output source voltage (VCCO), but

does not require the use of a reference voltage (VREF) or a

board termination voltage (VTT).

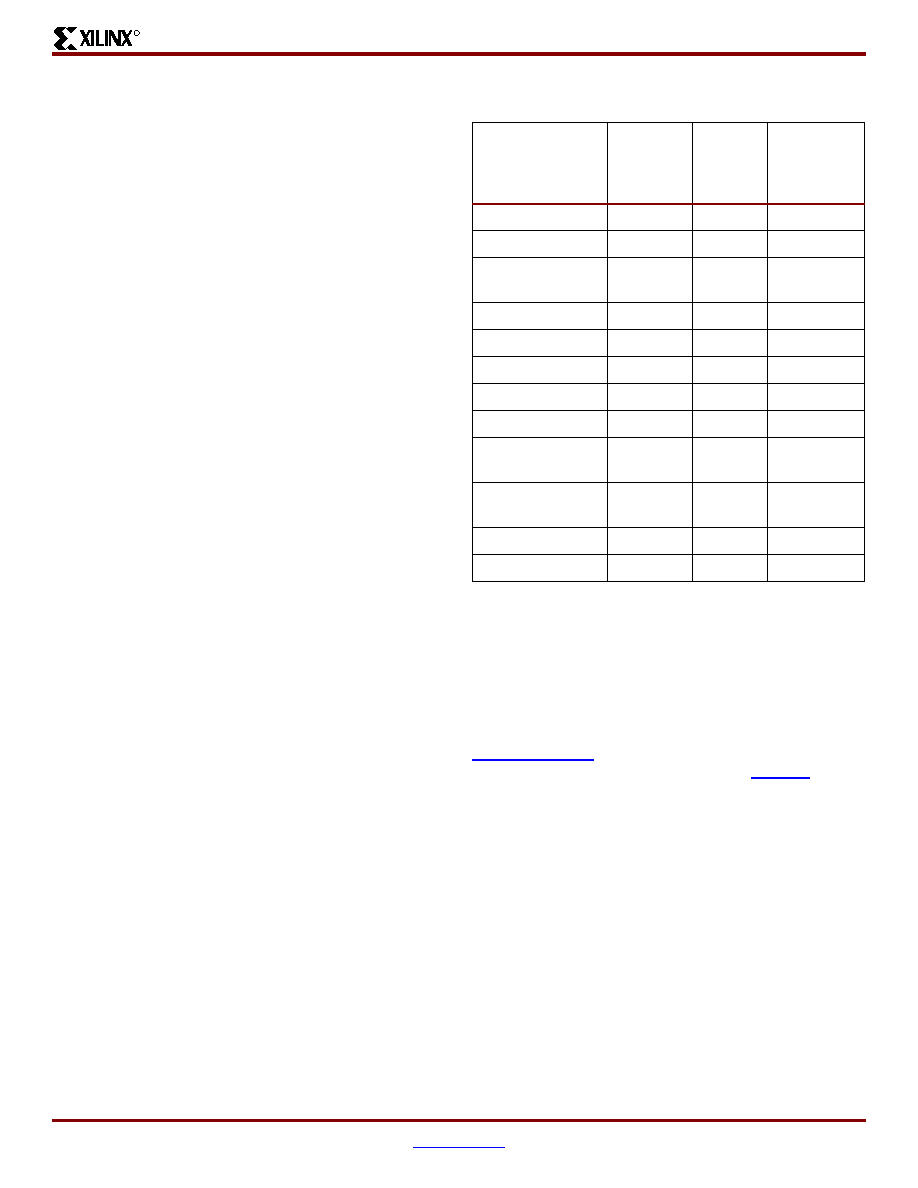

Table 15: Versatile I/O Supported Standards (Typical

Values)

I/O Standard

Input

Reference

Voltage

(VREF)

Output

Source

Voltage

(VCCO)

Board

Termination

Voltage

(VTT)

LVTTL (2-24 mA)

N/A

3.3

N/A

LVCMOS2

N/A

2.5

N/A

PCI (3V/5V,

33 MHz/66 MHz)

N/A

3.3

N/A

GTL

0.8

N/A

1.2

GTL+

1.0

N/A

1.5

HSTL Class I

0.75

1.5

0.75

HSTL Class III

0.9

1.5

HSTL Class IV

0.9

1.5

SSTL3 Class I

and II

1.5

3.3

1.5

SSTL2 Class I

and II

1.25

2.5

1.25

CTT

1.5

3.3

1.5

AGP-2X

1.32

3.3

N/A

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VI-27L-CW-F2 | CONVERTER MOD DC/DC 28V 100W |

| XC3S50AN-4TQG144C | IC SPARTAN-3AN FPGA 50K 144TQFP |

| XC3S50A-4FTG256C | IC SPARTAN-3A FPGA 50K 256FTBGA |

| VI-B5D-CX | CONVERTER MOD DC/DC 85V 75W |

| VI-27K-CW-F4 | CONVERTER MOD DC/DC 40V 100W |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2S30-5VQG100I | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 30K GATES 972 CELLS 263MHZ 2.5V 100VTQFP - Trays 制造商:Xilinx 功能描述:IC SYSTEM GATE |

| XC2S30-6CS144C | 功能描述:IC FPGA 2.5V C-TEMP 144-CSBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:Spartan®-II 標(biāo)準(zhǔn)包裝:40 系列:Spartan® 6 LX LAB/CLB數(shù):3411 邏輯元件/單元數(shù):43661 RAM 位總計(jì):2138112 輸入/輸出數(shù):358 門數(shù):- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應(yīng)商設(shè)備封裝:676-FBGA(27x27) |

| XC2S30-6CS144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II 2.5V FPGA Family:Introduction and Ordering Information |

| XC2S30-6CSG144C | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 30K GATES 972 CELLS 263MHZ 2.5V 144CSBGA - Trays |

| XC2S30-6CSG144I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-II FPGA Family |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。