- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄19665 > XC2C512-10FTG256C (Xilinx Inc)IC CR-II CPLD 512MCELL 256-FBGA PDF資料下載

參數(shù)資料

| 型號: | XC2C512-10FTG256C |

| 廠商: | Xilinx Inc |

| 文件頁數(shù): | 11/16頁 |

| 文件大小: | 0K |

| 描述: | IC CR-II CPLD 512MCELL 256-FBGA |

| 標準包裝: | 1 |

| 系列: | CoolRunner II |

| 可編程類型: | 系統(tǒng)內可編程 |

| 最大延遲時間 tpd(1): | 9.2ns |

| 電壓電源 - 內部: | 1.7 V ~ 1.9 V |

| 邏輯元件/邏輯塊數(shù)目: | 32 |

| 宏單元數(shù): | 512 |

| 門數(shù): | 12000 |

| 輸入/輸出數(shù): | 212 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 256-LBGA |

| 供應商設備封裝: | 256-FTBGA |

| 包裝: | 托盤 |

| 其它名稱: | 122-1407 |

CoolRunner-II CPLD Family

4

DS090 (v3.1) September 11, 2008

Product Specification

R

path. The BSC and ISP block has the JTAG controller and

In-System Programming Circuits.

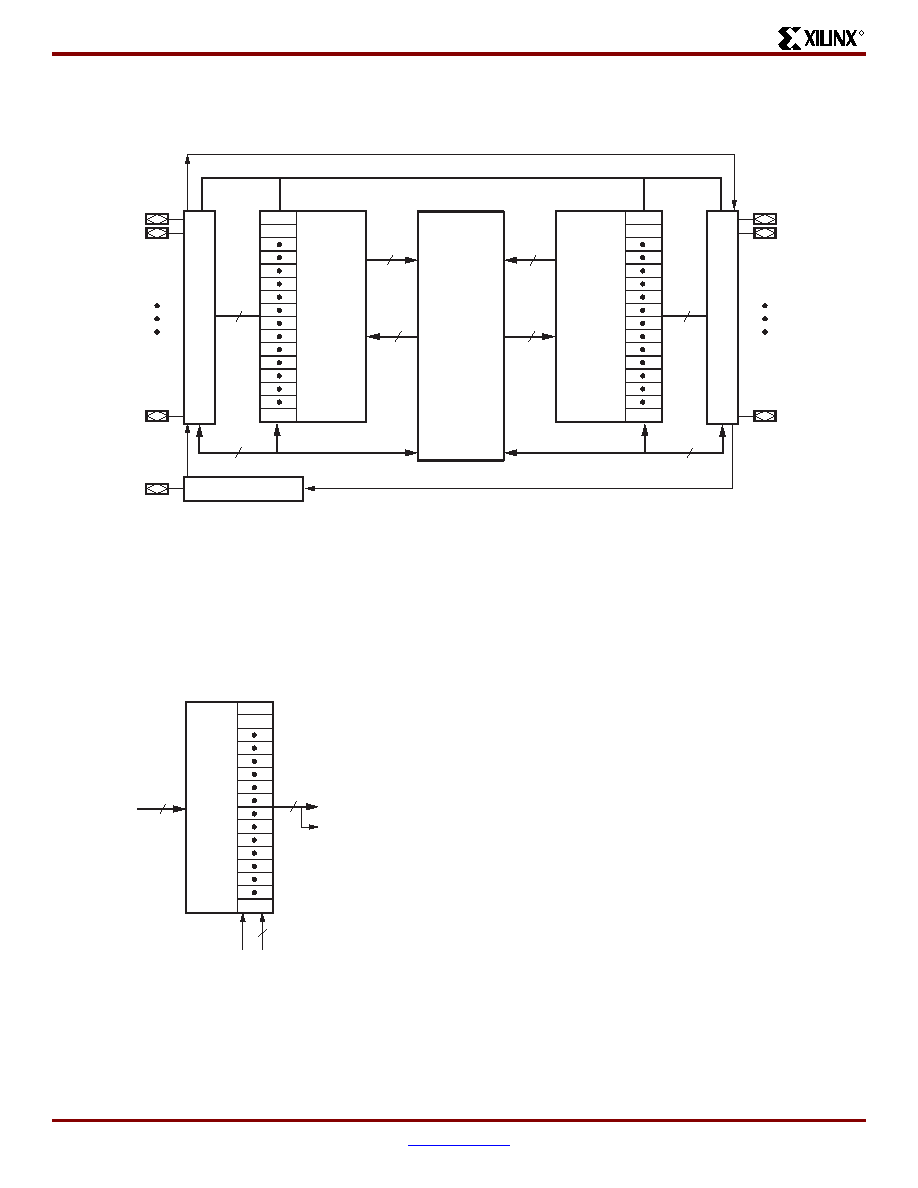

Function Block

The CoolRunner-II CPLD FBs contain 16 macrocells, with

40 entry sites for signals to arrive for logic creation and con-

nection. The internal logic engine is a 56 product term PLA.

All FBs, regardless of the number contained in the device,

are identical. For a high-level view of the FB, see Figure 2.

At the high level, the product terms (p-terms) reside in a

programmable logic array (PLA). This structure is extremely

flexible, and very robust when compared to fixed or cas-

caded product term FBs.

Classic CPLDs typically have a few product terms available

for a high-speed path to a given macrocell. They rely on

capturing unused p-terms from neighboring macrocells to

expand their product term tally, when needed. The result of

this architecture is a variable timing model and the possibil-

ity of stranding unusable logic within the FB.

The PLA is different — and better. First, any product term

can be attached to any OR gate inside the FB macrocell(s).

Second, any logic function can have as many p-terms as

needed attached to it within the FB, to an upper limit of 56.

Third, product terms can be re-used at multiple macrocell

OR functions so that within a FB, a particular logical product

need only be created once, but can be re-used up to 16

times within the FB. Naturally, this plays well with the fitting

software, which identifies product terms that can be shared.

The software places as many of those functions as it can

into FBs, so it happens for free. There is no need to force

macrocell functions to be adjacent or any other restriction

save residing in the same FB, which is handled by the soft-

ware. Functions need not share a common clock, common

set/reset, or common output enable to take full advantage of

the PLA. Also, every product term arrives with the same

time delay incurred. There are no cascade time adders for

putting more product terms in the FB. When the FB product

term budget is reached, there is a small interconnect timing

penalty to route signals to another FB to continue creating

logic. Xilinx design software handles all this automatically.

Figure 1: CoolRunner-II CPLD Architecture

Function

Block 1

Function

Block n

PLA

I/O

Blocks

I/O

Blocks

16

40

16 FB

16

I/O Pin

MC1

MC2

MC16

MC1

MC2

MC16

DS090_01_121201

AIM

I/O Pin

Direct Inputs

BSC and ISP

Clock and Control Signals

BSC Path

Direct Inputs

I/O Pin

JTAG

Figure 2: CoolRunner-II CPLD Function Block

PLA

16

40

3

MC1

Out

To AIM

Global

Clocks

Global

Set/Reset

MC2

MC16

DS090_02_101001

相關PDF資料 |

PDF描述 |

|---|---|

| MIC5219-3.3BML TR | IC REG LDO 3.3V .5A 6-MLF |

| GCC08DCMD | CONN EDGECARD 16POS .100" WW |

| TAJT106M006RNJ | CAP TANT 10UF 6.3V 20% 1210 |

| VE-B1H-CW-B1 | CONVERTER MOD DC/DC 52V 100W |

| EEC15DRXN | CONN EDGECARD 30POS DIP .100 SLD |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC2C512-10FTG256I | 功能描述:IC CR-II CPLD 512MCELL 256-FTBGA RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:CoolRunner II 標準包裝:40 系列:ispMACH® 4000C 可編程類型:系統(tǒng)內可編程 最大延遲時間 tpd(1):5.0ns 電壓電源 - 內部:1.65 V ~ 1.95 V 邏輯元件/邏輯塊數(shù)目:32 宏單元數(shù):512 門數(shù):- 輸入/輸出數(shù):128 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:176-LQFP 供應商設備封裝:176-TQFP(24x24) 包裝:托盤 |

| XC2C512-10PQ208C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 12K GATES 512 MCRCLLS 166MHZ COMM 0.18UM - Trays 制造商:Xilinx 功能描述:IC CRII CPLD 512MCRCELL 208PQFP |

| XC2C512-10PQ208I | 制造商:Xilinx 功能描述:CPLD COOLRUNNER-II 12K GATES 512 MCRCLLS 166MHZ IND 0.18UM 1 - Trays 制造商:Xilinx 功能描述:IC CRII CPLD 512MCRCELL 208PQFP 制造商:Xilinx 功能描述:IC CPLD 512MC 9.2NS 208PQFP |

| XC2C512-10PQG208C | 功能描述:IC CRII CPLD 512MCRCELL 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:CoolRunner II 標準包裝:90 系列:ispMACH® 4A 可編程類型:系統(tǒng)內可編程 最大延遲時間 tpd(1):7.5ns 電壓電源 - 內部:4.75 V ~ 5.25 V 邏輯元件/邏輯塊數(shù)目:- 宏單元數(shù):64 門數(shù):- 輸入/輸出數(shù):48 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:100-LQFP 供應商設備封裝:100-TQFP(14x14) 包裝:托盤 |

| XC2C512-10PQG208I | 功能描述:IC CR-II CPLD 512MCRCELL 208PQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:CoolRunner II 標準包裝:40 系列:ispMACH® 4000C 可編程類型:系統(tǒng)內可編程 最大延遲時間 tpd(1):5.0ns 電壓電源 - 內部:1.65 V ~ 1.95 V 邏輯元件/邏輯塊數(shù)目:32 宏單元數(shù):512 門數(shù):- 輸入/輸出數(shù):128 工作溫度:-40°C ~ 105°C 安裝類型:表面貼裝 封裝/外殼:176-LQFP 供應商設備封裝:176-TQFP(24x24) 包裝:托盤 |

發(fā)布緊急采購,3分鐘左右您將得到回復。