- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371269 > X68C75JM Port Expander and E2 Memory PDF資料下載

參數(shù)資料

| 型號: | X68C75JM |

| 英文描述: | Port Expander and E2 Memory |

| 中文描述: | 端口擴展和E2內(nèi)存 |

| 文件頁數(shù): | 3/26頁 |

| 文件大小: | 123K |

| 代理商: | X68C75JM |

3

X68C75 SLIC

E

2

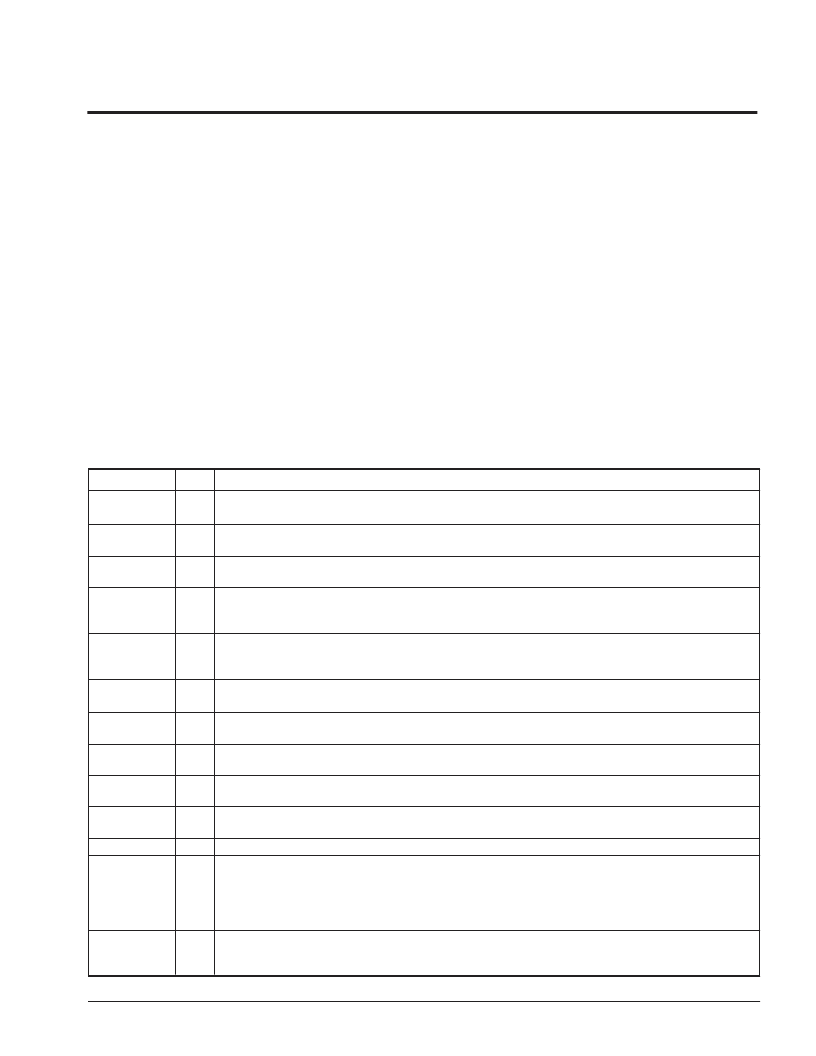

PIN DESCRIPTIONS

PIN NAME

I/O

DESCRIPTION

A

15

–A

8

I

Non-multiplexed high-order Address line inputs for the upper byte of the address. The addresses are

latched when AS makes a HIGH to LOW transition.

Multiplexed lower-order Address and DATA lines. The addresses are latched when AS makes a

HIGH to LOW transition.

Address Strobe input is used to latch the addresses present on the address lines A

15

–A

8

and AD

7

–

AD

0

into the device. The addresses are latched when AS transitions from HIGH to LOW.

The device select (CE) is an active HIGH input. This signal has to be asserted prior to AS HIGH to

LOW transition in order to generate a valid internal device select signal. Holding this pin LOW and

AS LOW will place the device in standby mode. The ports stay active at all times.

The E clock is the bus frequency clock input, and is used as a data timing reference signal. When

the E clock is LOW, the addresses are latched by HIGH to LOW transition on the AS pin. The E

clock HIGH cycle is used for data transfers.

The

IRQ

is an open-drain output. It can be configured to signal latching of new data into the ports,

and completion of

an E

2

memory write cycle.

The I/O lines of port A. The output driver can be configured as either CMOS or open-drain using the

AWO bit in CR. The I/O direction bit (DIRA) in CR is used to select the port A I/O mode.

The I/O lines of port B. The output driver can be configured as either CMOS or open-drain using the

BWO bit in CR. The I/O direction bit (DIRB) in CR is used to select the port B I/O mode.

The R/

W

signal indicates the direction of data transfers. During phase 2 (HIGH cycle) of the E clock,

the R/

W

is HIGH for a read, and LOW for a write cycle.

RESET

is used to initialize the internal static registers and has no effect on the E

2

memory opera-

tions. The default active level is LOW, but it can be reconfigured in EEM register.

The

SEL

input should be LOW for the device to be selected. This input is normaly tied to V

SS

.

The STRA controls port A and STRB controls port B. When ports are configured as inputs, a valid

transition on their strobe pins will latch into their Port Data Register the data present at the port input

pins. Writing to an output port Data Register generates a pulse of fixed duration on its corresponding

strobe pin. The output data presented at the output pins stay valid until the next data is written to the

output port data register.

WC

input has to be held LOW during a write cycle. It can be permanently tied HIGH in order to

disable writes to the E

2

memory. Taking the

WC

HIGH prior to t

BLC

(100

μ

s; the time delay from the

last write cycle to the start of internal programming cycle) will inhibit the write operation.

AD

7

–AD

0

I/O

AS

I

CE

I

E

I

IRQ

O

PA

7

–PA

0

I/O

PB

7

–PB

0

I/O

R/

W

I

RESET

I

SEL

STRA, STRB

I

I/O

WC

I

2899 PGM T01.1

The X68C75 write control input, serves as an external

control over the completion of a previously initiated page

load cycle.

The X68C75 also features the industry standard 5V E

2

memory characteristics such as byte or page mode write

and Toggle Bit Polling.

Read

A HIGH to LOW transition on AS latches the address;

the data will be output on the AD pins when E clock and

R/

W

are HIGH (t

ACC

).

Write

A write is performed by latching the address on the

falling edge of AS. The R/

W

signal LOW while E clock is

HIGH initiates a write cycle. The valid data must be

present on AD

0

-AD

7

prior to an E clock HIGH to LOW

transition. The data will be latched into the X68C75 on

the falling edge of E clock.

Page Write Operation

The X68C75 supports page mode write operations. This

allows the microcontroller to write from one to thirty-two

bytes of data to the X68C75. Each individual write within

a page write operation must conform to the byte write

timing requirements. The rising edge of E clock starts a

timer delaying the internal programming cycle 100

μ

s,

therefore, each successive write operation must begin

within 100

μ

s of the last byte written. The waveform

on page 19 illustrates the sequence and timing

requirements.

Toggle Bit Polling

Because the X68C75 typical write timing is less than the

specified 5ms, Toggle Bit Polling has been provided to

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X68C75L | Port Expander and E2 Memory |

| X68C75LI | Port Expander and E2 Memory |

| X68C75LM | Port Expander and E2 Memory |

| X68C75P | Port Expander and E2 Memory |

| X68C75PI | Port Expander and E2 Memory |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X68C75L | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75LI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75LM | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75P | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

| X68C75PI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Port Expander and E2 Memory |

發(fā)布緊急采購,3分鐘左右您將得到回復。