- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371267 > X5329V14Z-2.7A (INTERSIL CORP) EXT DIST RS232 DATA CBL DB25 FEMALE - DB25 FEMALE PDF資料下載

參數(shù)資料

| 型號(hào): | X5329V14Z-2.7A |

| 廠商: | INTERSIL CORP |

| 元件分類: | 電源管理 |

| 英文描述: | EXT DIST RS232 DATA CBL DB25 FEMALE - DB25 FEMALE |

| 中文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PDSO14 |

| 封裝: | ROHS COMPLIANT, PLASTIC, TSSOP-14 |

| 文件頁數(shù): | 2/21頁 |

| 文件大?。?/td> | 115K |

| 代理商: | X5329V14Z-2.7A |

X5328/X5329

Characteristics subject to change without notice.

2 of 21

REV 1.1.1 3/6/01

www.xicor.com

PIN DESCRIPTION

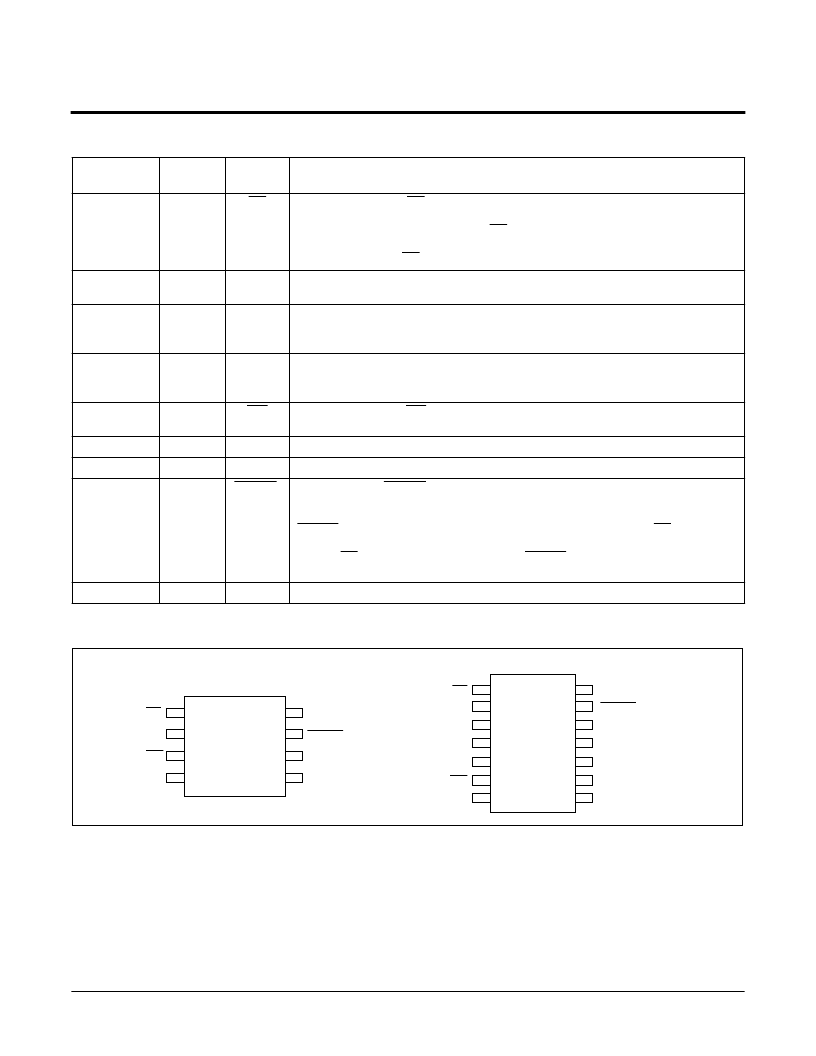

PIN CONFIGURATION

Pin

(SOIC/PDIP)

1

Pin

TSSOP

1

Name

CS

Function

Chip Select Input.

a high impedance state. Unless a nonvolatile write cycle is underway, the device

will be in the standby power mode. CS LOW enables the device, placing it in the

active power mode. Prior to the start of any operation after power up, a HIGH to

LOW transition on CS is required.

Serial Output.

SO is a push/pull serial data output pin. A read cycle shifts data out

on this pin. The falling edge of the serial clock (SCK) clocks the data out.

Serial Input.

SI is a serial data input pin. Input all opcodes, byte addresses, and

memory data on this pin. The rising edge of the serial clock (SCK) latches the input

data. Send all opcodes (Table 1), addresses and data MSB first.

Serial Clock.

The Serial Clock controls the serial bus timing for data input and out-

put. The rising edge of SCK latches in the opcode, address, or data bits present on

the SI pin. The falling edge of SCK changes the data output on the SO pin.

Write Protect.

The WP pin works in conjunction with a nonvolatile WPEN bit to

“l(fā)ock” the setting of the Watchdog Timer control and the memory write protect bits.

Ground

Supply Voltage

Reset Output

. RESET/RESET is an active LOW/HIGH, open drain output

which goes active whenever V

CC

falls below the minimum V

will remain active until V

CC

rises above the minimum V

RESET/RESET goes active if the Watchdog Timer is enabled and CS remains

either HIGH or LOW longer than the selectable Watchdog time out period. A falling

edge of CS will reset the Watchdog Timer. RESET/RESET goes active on power

up at about 1V and remains active for 200ms after the power supply stabilizes.

No internal connections

CS HIGH, deselects the device and the SO output pin is at

2

2

SO

5

8

SI

6

9

SCK

3

6

WP

4

8

7

7

14

13

V

V

SS

CC

RESET/

RESET

CC

sense level. It

sense level for 200ms.

CC

3-5,10-12

NC

8-Lead SOIC/PDIP

CS

WP

SO

1

2

3

4

RESET/RESET

8

7

6

5

14-Lead TSSOP

SO

NC

WP

V

SS

1

2

3

4

5

6

7

RESET/RESET

SCK

SI

14

13

12

11

10

9

8

V

CC

NC

X5328/29

V

CC

SCK

SI

CS

NC

NC

NC

NC

X5328/29

V

CC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X5329S8 | RTC Module With CPU Supervisor |

| X5329S8Z-2.7A | RTC Module With CPU Supervisor |

| X5329PZ-2.7A | RTC Module With CPU Supervisor |

| X5329PZ-4.5A | RTC Module With CPU Supervisor |

| X5329S8-2.7A | RTC Module With CPU Supervisor |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X5329V14Z-4.5A | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:CPU Supervisor with 32Kbit SPI EEPROM |

| X533 | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:3.3V SURFACE MOUNT 5.0 x 7.5mm LVDS CLOCK OSCILLATOR |

| X533-333.00M | 制造商:CONNOR-WINFIELD 制造商全稱:Connor-Winfield Corporation 功能描述:3.3V SURFACE MOUNT 5.0 x 7.5mm LVDS CLOCK OSCILLATOR |

| X540T2 914248 | 制造商:Intel 功能描述:ETHERNETCONVERGED NETWORK ADAPTER - Boxed Product (Development Kits) |

| X540T2BLK 927245 | 制造商:Intel 功能描述:TWIN POND T2 ETHERNET CONVERGED NETWORK ADAPTER - Boxed Product (Development Kits) |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。