- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371253 > X4043P8 10NS, PDIP, COM TEMP(EPLD) PDF資料下載

參數(shù)資料

| 型號(hào): | X4043P8 |

| 英文描述: | 10NS, PDIP, COM TEMP(EPLD) |

| 中文描述: | 模擬IC |

| 文件頁(yè)數(shù): | 6/25頁(yè) |

| 文件大小: | 144K |

| 代理商: | X4043P8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)當(dāng)前第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

X4043/45

Characteristics subject to change without notice.

6 of 25

REV 1.1.17 9/14/01

www.xicor.com

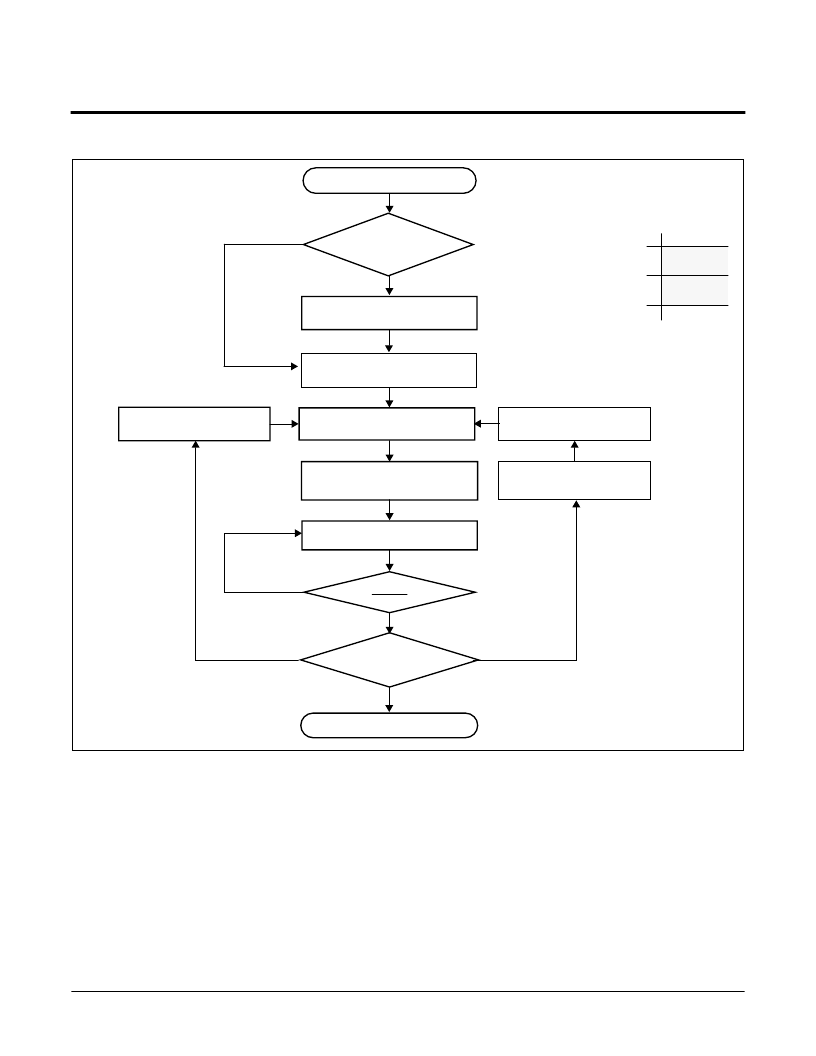

Figure 5. V

TRIP

Programming Sequence

V

TRIP

Programming

Power Down

the Device

Actual V

TRIP

–

Desired V

TRIP

= Error

DONE

Set Higher V

TRIP

Sequence

Error < MDE

–

| Error | < | MDE |

YES

NO

Error > MDE

+

Desired

V

TRIP

<

Present Value

Execute

No

YES

Execute

V

TRIP

Reset Sequence

Set V

CC

= desired V

TRIP

New V

CC

applied =

Old V

CC

applied + | Error |

New V

CC

applied =

Old V

CC

applied – | Error |

Execute Reset V

TRIP

Sequence

Output Switches

(RESET)

Let:

MDE = Maximum Desired Error

MDE

+

Desired Value

MDE

–

Acceptable

Error Range

Error = Actual – Desired

Ramp V

CC

Control Register

The control register provides the user a mechanism for

changing the block lock and watchdog timer settings.

The block lock and watchdog timer bits are nonvolatile

and do not change when power is removed.

The control register is accessed with a special pream-

ble in the slave byte (1011) and is located at address

1FFh. It can only be modified by performing a byte

write operation directly to the address of the register

and only one data byte is allowed for each register

write operation. Prior to writing to the control register,

the WEL and RWEL bits must be set using a two step

process, with the whole sequence requiring 3 steps.

See "Writing to the Control Register".

The user must issue a stop after sending this byte to

the register to initiate the nonvolatile cycle that stores

WD1, WD0, BP2, BP1, and BP0. The X4043/45 will not

acknowledge any data bytes written after the first byte

is entered.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X4043P8-2.7 | Analog IC |

| X4043P8-2.7A | F22V10C FAMILY,500 GATE SPLD,5V,24-PIN(EPLD) |

| X4043P8-4.5A | 10NS, TSSOP, IND TEMP(EPLD) |

| X4043P8I | 15NS, PLCC, IND TEMP(EPLD) |

| X4043P8I-2.7 | Analog IC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X4043P8-2.7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| X4043P8-2.7A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| X4043P8-4.5A | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| X4043P8I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

| X4043P8I-2.7 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog IC |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。