- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371216 > X25401SM SPI Serial AUTOSTORE⑩ NOVRAM PDF資料下載

參數(shù)資料

| 型號: | X25401SM |

| 英文描述: | SPI Serial AUTOSTORE⑩ NOVRAM |

| 中文描述: | SPI串行自動(dòng)存儲⑩NOVRAM |

| 文件頁數(shù): | 3/14頁 |

| 文件大小: | 57K |

| 代理商: | X25401SM |

X25401

3

DEVICE OPERATION

The X25401 contains an 8-bit instruction register. It is

accessed via the SI input, with data being clocked in on

the rising edge of SCK.

CS

must be LOW during the

entire data transfer operation.

Table 1 contains a list of the instructions and their

operation codes. The most significant bit (MSB) of all

instructions is a logic one (HIGH), bits 6 through 3 are

either RAM address bits (A) or don’t cares (X) and bits

2 through 0 are the operation codes. The X25401

requires the instruction to be shifted in with the MSB

first.

After

CS

is LOW, the X25401 will not begin to interpret

the data stream until a logic “1” has been shifted in on

SI. Therefore,

CS

may be brought LOW with SCK

running and SI LOW. SI must then go HIGH to indicate

the start condition of an instruction before the X25401

will begin any action.

In addition, the SCK clock is totally static. The user can

completely stop the clock and data shifting will be

stopped. Restarting the clock will resume shifting of

data.

RCL and

RECALL

Either a software RCL instruction or a LOW on the

RECALL

input will initiate a transfer of E

2

PROM data

into RAM. This software or hardware recall operation

sets an internal “previous recall” latch. This latch is

reset upon power-up and must be intentionally set by

the user to enable any write or store operations. Al-

though a recall operation is performed upon power-up,

the previous recall latch is not set by this operation.

WRDS and WREN

Internally the X25401 contains a “write enable” latch.

This latch must be set for either writes to the RAM or

store operations to the E

2

PROM. The WREN instruction

sets the latch and the WRDS instruction resets the latch,

disabling both RAM writes and E

2

PROM stores, effec-

tively protecting the nonvolatile data from corruption. The

write enable latch is automatically reset on power-up.

STO

The software STO instruction will initiate a transfer of

data from RAM to E

2

PROM. In order to safeguard

against unwanted store operations, the following con-

ditions must be true:

STO instruction issued.

The internal “write enable” latch must be set

(WREN instruction issued).

The “previous recall” latch must be set (either a

software or hardware recall operation).

Once the store cycle is initiated, all other device func-

tions are inhibited. Upon completion of the store cycle,

the write enable latch is reset. Refer to Figure 4 for a

state diagram description of enabling/disabling condi-

tions for store operations.

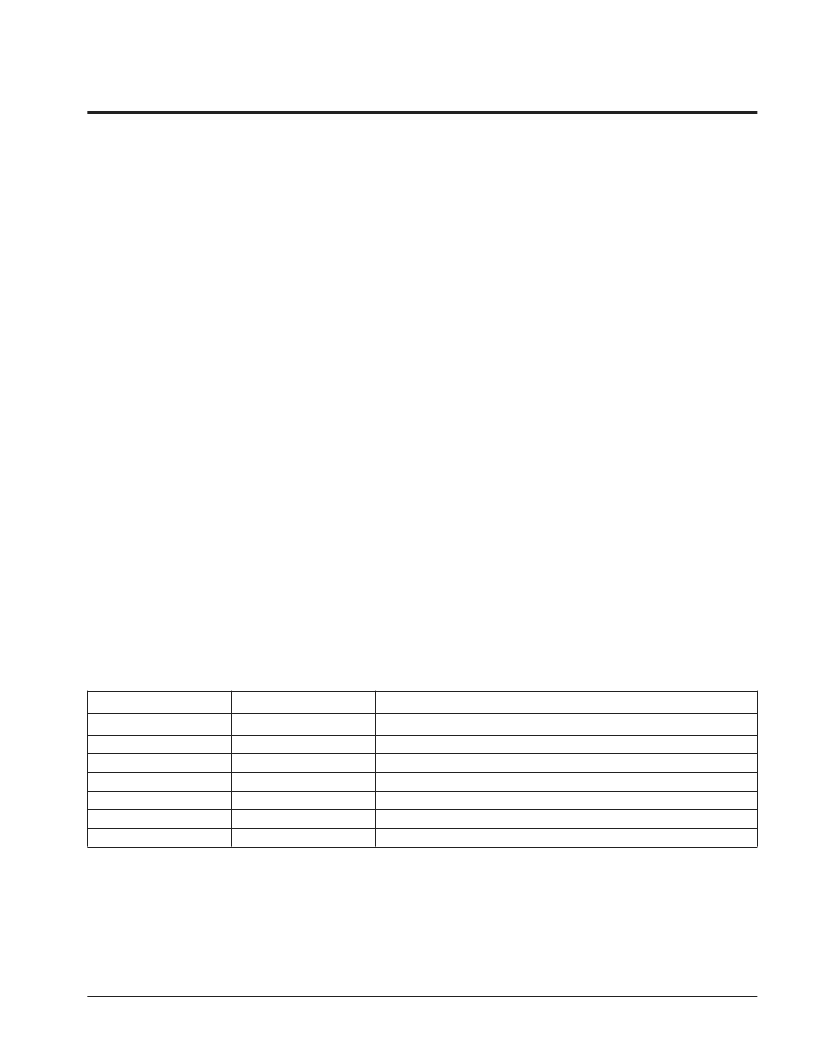

TABLE 1. INSTRUCTION SET

Instruction

Format, I

2

I

1

I

0

1XXXX000

1XXXX001

1XXXX010

1AAAA011

1XXXX100

1XXXX101

1AAAA11X

Operation

WRDS (Figure 3)

STO (Figure 3)

ENAS

WRITE (Figure 2)

WREN (Figure 3)

RCL (Figure 3)

READ (Figure 1)

Reset Write Enable Latch (Disables Writes and Stores)

Store RAM Data in E

2

PROM

Enable AUTOSTORE Feature

Write Data into RAM Address AAAA

Set Write Enable Latch (Enables Writes and Stores)

Recall E

2

PROM Data into RAM

Read Data from RAM Address AAAA

2051 PGM T11

X = Don’t Care

A = Address

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25642PM-2.7 | CAP,Non-Specified,20uF,10-% Tol,10+% Tol |

| X25642SI-2.7 | Advanced SPI Serial E 2 PROM with Block Lock TM Protection |

| X25642SM-2.7 | Advanced SPI Serial E 2 PROM with Block Lock TM Protection |

| X25642S8 | Advanced SPI Serial E 2 PROM with Block Lock TM Protection |

| X25642S8I | Advanced SPI Serial E 2 PROM with Block Lock TM Protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25640 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:Advanced SPI Serial E2PROM With Block LockTM Protection |

| X25640S | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:IC-SM-64K SERIAL EEPROM+SPI |

| X25642 | 制造商:ICMICR 功能描述: |

| X25642F | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:Advanced SPI Serial E2PROM with Block Lock Protection |

| X25642FG | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:Advanced SPI Serial E2PROM with Block Lock Protection |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。