- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371215 > X25320V SPI Serial E2PROM With Block LockTM Protection PDF資料下載

參數(shù)資料

| 型號: | X25320V |

| 英文描述: | SPI Serial E2PROM With Block LockTM Protection |

| 中文描述: | SPI串行E2PROM的保護帶座LockTM |

| 文件頁數(shù): | 3/15頁 |

| 文件大小: | 70K |

| 代理商: | X25320V |

X25320

3

PRINCIPLES OF OPERATION

The X25320 is a 4K x 8 E

2

PROM designed to interface

directly with the synchronous serial peripheral interface

(SPI) of many popular microcontroller families.

The X25320 contains an 8-bit instruction register. It is

accessed via the SI input, with data being clocked in on

the rising SCK.

CS

must be LOW and the

HOLD

and

WP

inputs must be HIGH during the entire operation. The

WP

input is “Don’t Care” if WPEN is set “0”.

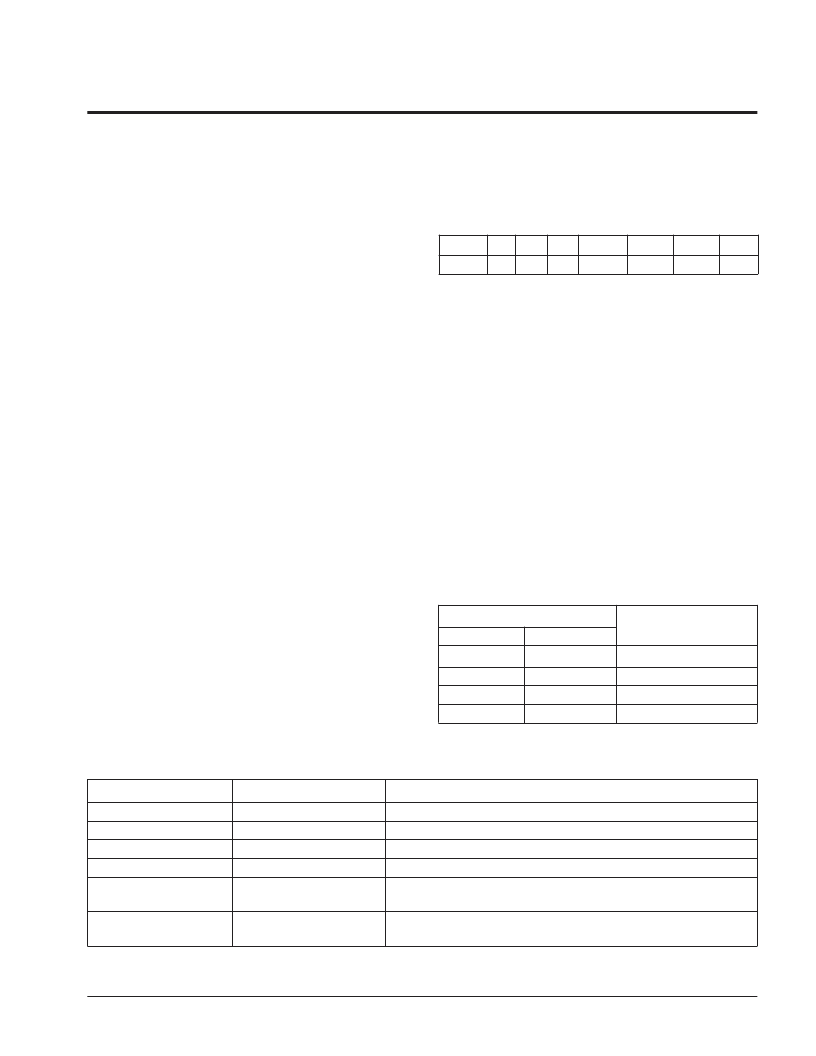

Table 1 contains a list of the instructions and their

opcodes. All instructions, addresses and data are trans-

ferred MSB first.

Data input is sampled on the first rising edge of SCK after

CS

goes LOW. SCK is static, allowing the user to stop

the clock and then resume operations. If the clock line is

shared with other peripheral devices on the SPI bus, the

user can assert the

HOLD

input to place the X25320 into

a “PAUSE” condition. After releasing

HOLD

, the X25320

will resume operation from the point when

HOLD

was

first asserted.

Write Enable Latch

The X25320 contains a “write enable” latch. This latch

must be SET before a write operation will be completed

internally. The WREN instruction will set the latch and

the WRDI instruction will reset the latch. This latch is

automatically reset upon a power-up condition and after

the completion of a byte, page, or status register write

cycle.

Status Register

The RDSR instruction provides access to the status

register. The status register may be read at any time,

even during a write cycle. The status register is format-

ted as follows:

WPEN, BP0 and BP1 are set by the WRSR instruction.

WEL and WIP are read-only and automatically set by

other operations.

The Write-In-Process (WIP) bit indicates whether the

X25320 is busy with a write operation. When set to a “1”,

a write is in progress, when set to a “0”, no write is in

progress. During a write, all other bits are set to “1”.

The Write Enable Latch (WEL) bit indicates the status of

the “write enable” latch. When set to a “1”, the latch is set,

when set to a “0”, the latch is reset.

The Block Protect (BP0 and BP1) bits are nonvolatile

and allow the user to select one of four levels of protec-

tion. The X25320 is divided into four 8192-bit segments.

One, two, or all four of the segments may be protected.

That is, the user may read the segments but will be

unable to alter (write) data within the selected segments.

The partitioning is controlled as illustrated below.

Status Register Bits

BP1

Array Addresses

Protected

BP0

0

0

1

1

0

1

0

1

None

$0C00–$0FFF

$0800–$0FFF

$0000–$0FFF

3063 PGM T03

Table 1. Instruction Set

Instruction Name

WREN

WRDI

RDSR

WRSR

Instruction Format*

0000 0110

0000 0100

0000 0101

0000 0001

Operation

Set the Write Enable Latch (Enable Write Operations)

Reset the Write Enable Latch (Disable Write Operations)

Read Status Register

Write Status Register

Read Data from Memory Array beginning at selected

address

Write Data to Memory Array beginning at Selected Address

(1 to 32 Bytes)

READ

0000 0011

WRITE

0000 0010

3063 PGM T04

*Instructions are shown MSB in leftmost position. Instructions are transferred MSB first.

7

6

X

5

X

4

X

3

2

1

0

WPEN

BP1

BP0

WEL

WIP

3063 PGM T02

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25320V-2.7 | SPI Serial E2PROM With Block LockTM Protection |

| X25320VI | SPI Serial E2PROM With Block LockTM Protection |

| X25320VM | SPI Serial E2PROM With Block LockTM Protection |

| X25320P | SPI Serial E2PROM With Block LockTM Protection |

| X25320P-2.7 | SPI Serial E2PROM With Block LockTM Protection |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25320V-2.7 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25320VG | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25320VG-2.7 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25320VI | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:SPI Serial E2PROM With Block LockTM Protection |

| X25320VI-2.7 | 制造商:ICMIC 制造商全稱:IC MICROSYSTEMS 功能描述:SPI Serial E2PROM With Block LockTM Protection |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。