- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄371217 > X25163V14I-1.8 25FT TWINAX CABLE PDF資料下載

參數(shù)資料

| 型號(hào): | X25163V14I-1.8 |

| 英文描述: | 25FT TWINAX CABLE |

| 中文描述: | 可編程看門(mén)狗定時(shí)器 |

| 文件頁(yè)數(shù): | 5/16頁(yè) |

| 文件大小: | 76K |

| 代理商: | X25163V14I-1.8 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)當(dāng)前第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

X25643/45

X25323/25

X25163/65

5

0

1

2

3

4

5

6

7

8

9

10

20 21 22 23 24 25

26 27 28 29 30

7

6

5

4

3

2

1

0

DATA OUT

CS

SCK

SI

SO

MSB

HIGH IMPEDANCE

INSTRUCTION

16 BIT ADDRESS

15 14 13

3

2

1

0

7036 FRM 03

For the Page Write Operation (byte or page write) to be

completed, CS can only be brought HIGH after bit 0 of the

last data byte to be written is clocked in. If it is brought

HIGH at any other time, the write operation will not be

completed (Figure 4).

To write to the Status Register, the WRSR instruction is

followed by the data to be written (Figure 5). Data bits 0

and 1 must be “0” .

While the write is in progress following a Status Register

or E

PROM Sequence, the Status Register may be read

to check the WIP bit. During this time the WIP bit will be

high.

2

RESET/RESET Operation

The RESET (X25xx3) output is designed to go LOW

whenever V

CC

has dropped below the minimum trip point

and/or the Watchdog timer has reached its programmable

time-out limit.

The RESET (X25xx5) output is designed to go HIGH

whenever V

CC

has dropped below the minimum trip point

and/or the watchdog timer has reached its programmable

time-out limit.

The RESET/RESET output is an open drain output and

requires a pull up resistor.

Operational Notes

The device powers-up in the following state:

The device is in the low power standby state.

A HIGH to LOW transition on CS is required to enter an

active state and receive an instruction.

SO pin is high impedance.

The Write Enable Latch is reset.

The Flag Bit is reset.

Reset Signal is active for t

PURST

.

Data Protection

The following circuitry has been included to prevent inad-

vertent writes:

A WREN instruction must be issued to set the Write

Enable Latch.

CS must come HIGH at the proper clock count in order

to start a nonvolatile write cycle.

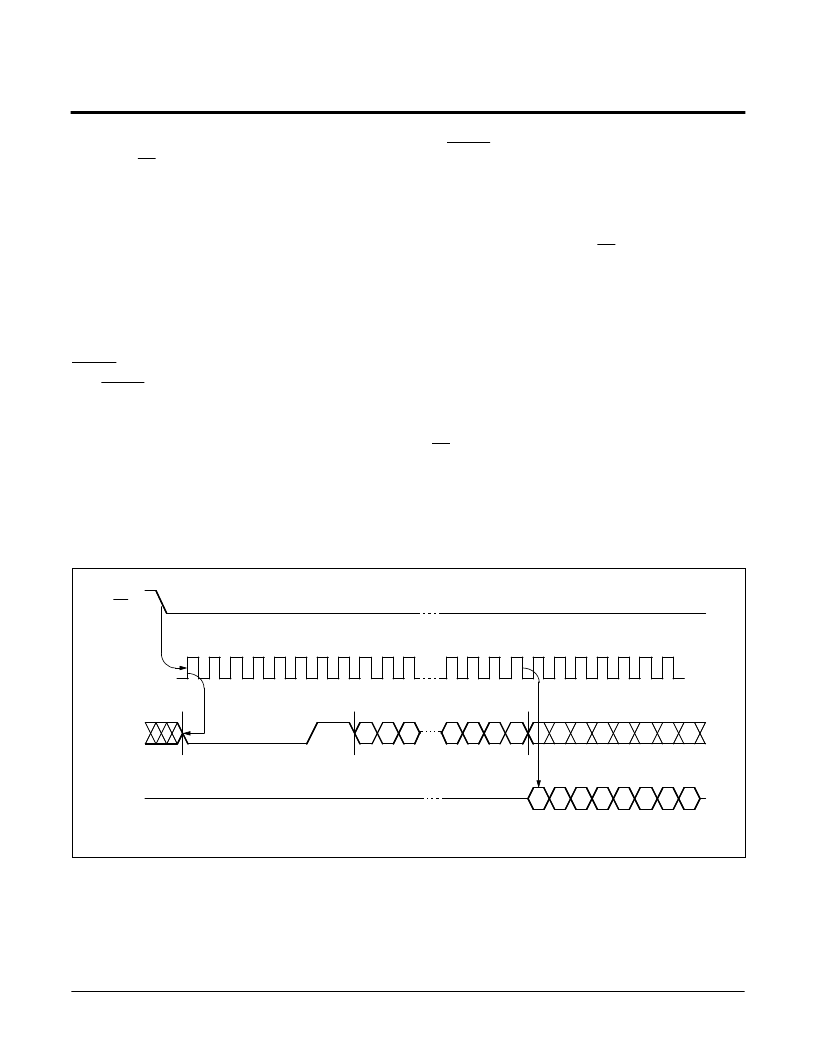

Figure 1. Read E

2

PROM Array Sequence

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X25165V14I-1.8 | 50FT TWINAX CABLE SCA-7362267-050 |

| X25643S8-1.8 | Programmable Watchdog Timer & V CC Supervisory Circuit w/Serial E 2 PROM |

| X25643S14 | Programmable Watchdog Timer & V CC Supervisory Circuit w/Serial E 2 PROM |

| X25643S14-1.8 | Programmable Watchdog Timer & V CC Supervisory Circuit w/Serial E 2 PROM |

| X25643S14-2.7 | Programmable Watchdog Timer & V CC Supervisory Circuit w/Serial E 2 PROM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X25163V14I-2.7 | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:Programmable Watchdog Timer & V CC Supervisory Circuit w/Serial E 2 PROM |

| X25164 | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:Programmable Watchdog Timer w/Serial E 2 PROM |

| X25164S14 | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:Programmable Watchdog Timer w/Serial E 2 PROM |

| X25164S14-1.8 | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:Programmable Watchdog Timer w/Serial E 2 PROM |

| X25164S14-2.7 | 制造商:XICOR 制造商全稱(chēng):Xicor Inc. 功能描述:Programmable Watchdog Timer w/Serial E 2 PROM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。