- 您現(xiàn)在的位置:買賣IC網 > PDF目錄140363 > WS512K32-55G1UQ 512K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 PDF資料下載

參數(shù)資料

| 型號: | WS512K32-55G1UQ |

| 元件分類: | SRAM |

| 英文描述: | 512K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 |

| 封裝: | CERAMIC, QFP-68 |

| 文件頁數(shù): | 5/10頁 |

| 文件大小: | 150K |

| 代理商: | WS512K32-55G1UQ |

4

White Electronic Designs Corporation (602) 437-1520 www.whiteedc.com

WS512K32-XXX

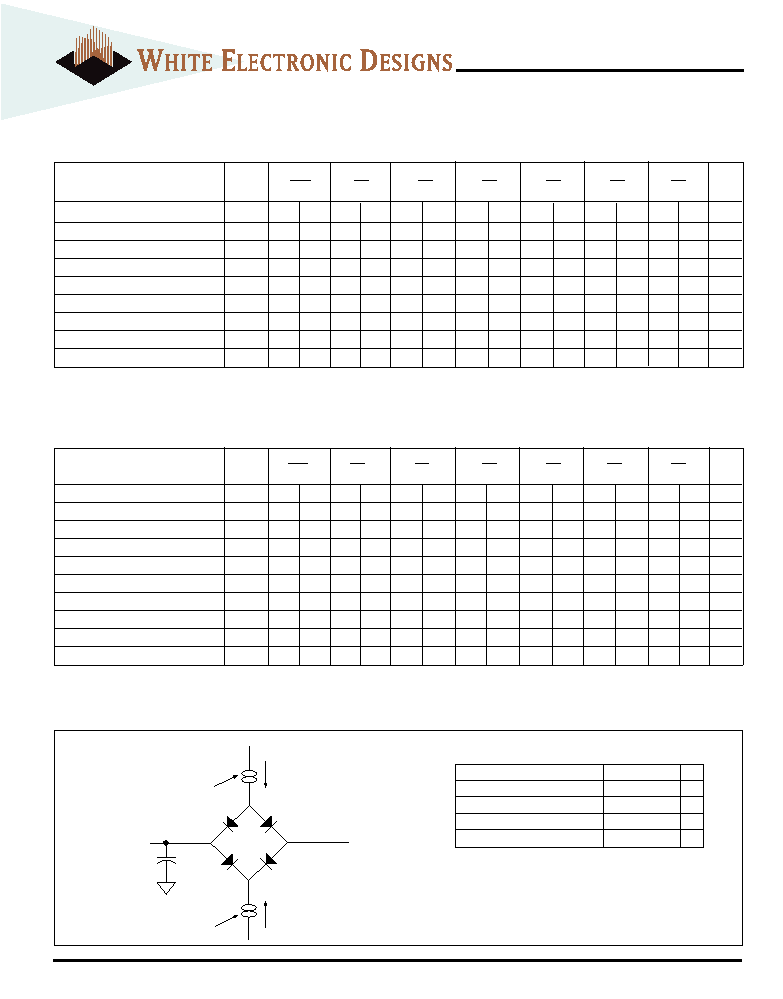

AC CHARACTERISTICS

(VCC = 5.0V, VSS = 0V, TA = -55

°C to +125°C)

FIG. 4

AC TEST CIRCUIT

NOTES:

VZ is programmable from -2V to +7V.

IOL & IOH programmable from 0 to 16mA.

Tester Impedance Z0 = 75

.

VZ is typically the midpoint of VOH and VOL.

IOL & IOH are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

I

Current Source

D.U.T.

C

= 50 pf

eff

I

OL

V

≈ 1.5V

(Bipolar Supply)

Z

Current Source

OH

AC CHARACTERISTICS

(VCC = 5.0V, VSS = 0V, TA = -55

°C to +125°C)

AC TEST CONDITIONS

Parameter

Typ

Unit

Input Pulse Levels

VIL = 0, VIH = 3.0

V

Input Rise and Fall

5

ns

Input and Output Reference Level

1.5

V

Output Timing Reference Level

1.5

V

Parameter

Symbol

-15*

-17

-20

-25

-35

-45

-55

Units

Write Cycle

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min Max

Write Cycle Time

tWC

15

17

20

25

35

45

55

ns

Chip Select to End of Write

tCW

13

15

17

25

35

50

ns

Address Valid to End of Write

tAW

13

15

17

25

35

50

ns

Data Valid to End of Write

tDW

10

11

12

13

20

25

ns

Write Pulse Width

tWP

13

15

17

25

35

40

ns

Address Setup Time

tAS

2

222

2

ns

Address Hold Time

tAH

0

000

0

5

ns

Output Active from End of Write

tOW1

2

234

4

5

ns

Write Enable to Output in High Z

tWHZ1

8

9

11

13

15

20

ns

Data Hold Time

tDH

0

000

0

ns

* 15ns Access Time available only in Commercial and Industrial Temperature. This speed is not fully characterized and is subject to change without notice.

1. This parameter is guaranteed by design but not tested.

2. The Address Setup Time of minimum 2ns is for the G2T, G1U and H1 packages. tAS minimum for the G4T package is 0ns.

Parameter

Symbol

-15*

-17

-20

-25

-35

-45

-55

Units

Read Cycle

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Min

Max

Read Cycle Time

tRC

15

17

20

25

35

45

55

ns

Address Access Time

tAA

15

17

20

25

35

45

55

ns

Output Hold from Address Change

tOH

0

0000

0

ns

Chip Select Access Time

tACS

15

17

20

25

35

45

55

ns

Output Enable to Output Valid

tOE

8

9

10

12

25

ns

Chip Select to Output in Low Z

tCLZ1

2

2244

4

ns

Output Enable to Output in Low Z

tOLZ1

0

0000

0

ns

Chip Disable to Output in High Z

tCHZ1

12

15

20

ns

Output Disable to Output in High Z

tOHZ1

12

15

20

ns

* 15ns Access Time available only in Commercial and Industrial Temperature. This speed is not fully characterized and is subject to change without notice.

1. This parameter is guaranteed by design but not tested.

相關PDF資料 |

PDF描述 |

|---|---|

| WS512K32L-17G1UMA | 512K X 32 MULTI DEVICE SRAM MODULE, 17 ns, CQFP68 |

| WS512K32L-17G1UQ | 512K X 32 MULTI DEVICE SRAM MODULE, 17 ns, CQFP68 |

| WMS128K8C-120DEMEA | 128K X 8 STANDARD SRAM, 120 ns, CDSO32 |

| WMS512K8V-20CIA | 512K X 8 STANDARD SRAM, 20 ns, CDIP32 |

| WMS512K8V-20CLIA | 512K X 8 STANDARD SRAM, 20 ns, CQCC32 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| WS512K32-55G2I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 SRAM Module |

| WS512K32-55G2M | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 SRAM Module |

| WS512K32-55G2Q | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 SRAM Module |

| WS512K32-55G2TC | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:SRAM|512KX32|CMOS|QFP|68PIN|CERAMIC |

| WS512K32-55G2TCA | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x32 SRAM Module |

發(fā)布緊急采購,3分鐘左右您將得到回復。