- 您現(xiàn)在的位置:買賣IC網 > PDF目錄361787 > W551C040 Interactive Toy Family PDF資料下載

參數資料

| 型號: | W551C040 |

| 英文描述: | Interactive Toy Family |

| 中文描述: | 互動玩具系列 |

| 文件頁數: | 7/15頁 |

| 文件大小: | 127K |

| 代理商: | W551C040 |

W551Cxxx Data Sheet

Winbond Electronics Corp.

6

Release Date:

January 2, 2001

Function Description

3.1 W551Cxxx Functional Description

The maximum number of the ADDR clock is 24 bits. The address data is shifted into the 24 bits address counter

by the ADDR clock. The MSB x bits of the address counter are the page codes, and the rest (24 - x) bits are the bit

of address. Note that the MSB is shifted first. The MSB 5 bits of the address counter are always gating (exclusive

OR) with the content of the page-code cells to determine whether these two articles are match or not. Only when the

page codes are matched with the content of the page-code cells, this device can be enabled. The counting source of

the address counter is the CLK clock, the falling edge signal of the CLK clock up-count the counter.

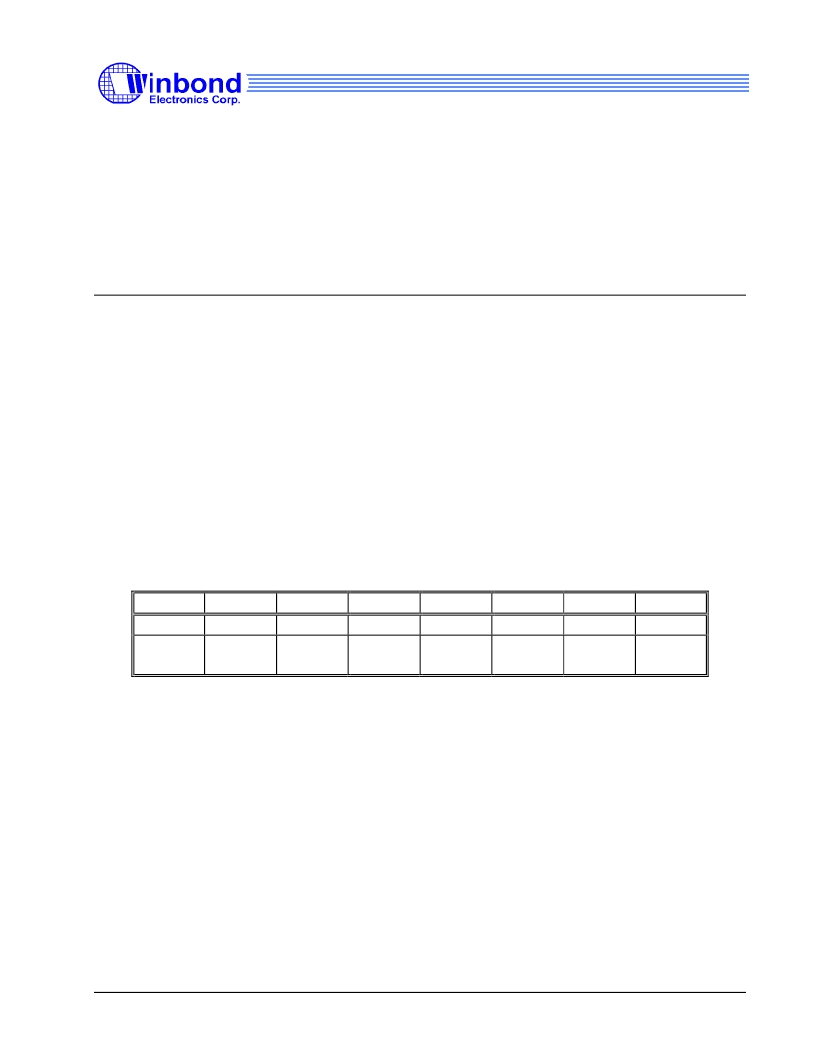

In normal-read mode the ADDR and CLK clock cannot be active simultaneously. The first rising edge signal of

the ADDR clock after CLK clocking will reset the address shift registers. The following table describes the needed

bits of

″

page code

″

:

Part #

W551C002

W551C005

W551C010

W551C020

W551C040

W551C060

W551C080

Density

256K bits

512K bits

1M bits

2M bits

4M bits

6M bits

8M bits

Bits of

page code

6

5

4

3

2

2

1

相關PDF資料 |

PDF描述 |

|---|---|

| W551C060 | Interactive Toy Family |

| W551C080 | Interactive Toy Family |

| W5560-11 | |

| W5560-13 | |

| W5560-21 | |

相關代理商/技術參數 |

參數描述 |

|---|---|

| W551C060 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:Serial Voice Memory |

| W551C080 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:Serial Voice Memory |

| W55412A | 制造商:WINBOND 制造商全稱:Winbond 功能描述:VOICE PROM (256K OTP) |

| W55F01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:EEPROM |

| W55F05 | 制造商:WINBOND 制造商全稱:Winbond 功能描述:SERIAL FLASH EEPROM SERIES |

發(fā)布緊急采購,3分鐘左右您將得到回復。