- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359452 > VV5404 (Electronic Theatre Controls, Inc.) CIF FORMAT DIGITAL IMAGE SENSOR PDF資料下載

參數(shù)資料

| 型號(hào): | VV5404 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | CIF FORMAT DIGITAL IMAGE SENSOR |

| 中文描述: | CIF格式的數(shù)字圖像傳感器 |

| 文件頁(yè)數(shù): | 27/54頁(yè) |

| 文件大小: | 786K |

| 代理商: | VV5404 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)當(dāng)前第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)

VV5404 & VV6404

CD5404-6404F-A

27/54

5.

Serial Control Bus

5.1

Writing configuration information to the video sensor and reading both sensor status and configuration information

back from the sensor is performed via the 2-wire serial interface.

Communication using the serial bus centres around a number of registers internal to the video sensor. These

registers store sensor status, set-up, exposure and system information. Most of the registers are read/write allowing

the receiving equipment to change their contents. Others (such as the chip id) are read only.

The main features of the serial interface include:

Variable length read/write messages.

Indexed addressing of information source or destination within the sensor.

Automatic update of the index after a read of write message.

Message abort with negative acknowledge from the master.

Byte oriented messages.

The contents of all internal registers accessible via the serial control bus are encapsulated in each start-of-field line -

see Section 4.3.4.

General Description

5.2

The video processor must perform the role of a communications master and the camera acts as either a slave receiver

or transmitter.The communication from host to camera takes the form of 8-bit data with a maximum serial clock video

processor frequency of up to 100 kHz. Since the serial clock is generated by the host it determines the data transfer

rate. The bus address for the sensor in VV6404 is 20

H

and for the serial E

2

PROM containing the defect map it is A0

H

.

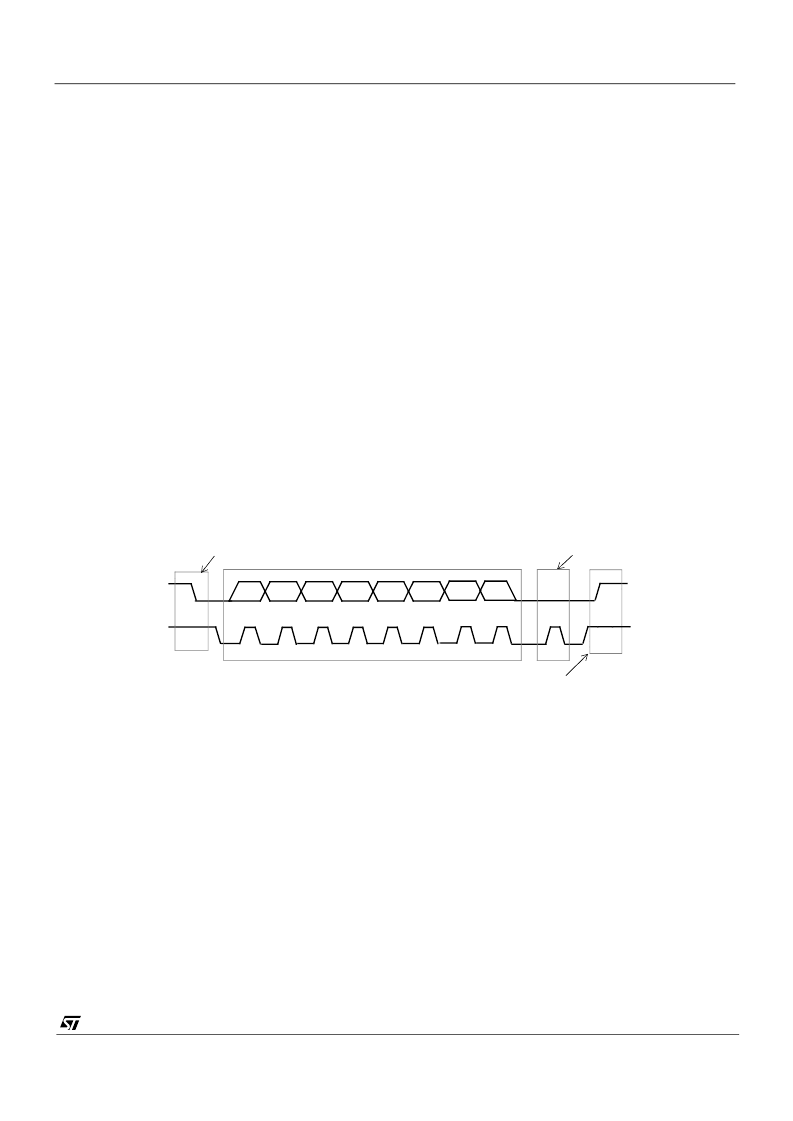

Data transfer protocol on the bus is shown below.

Serial Communication Protocol

5.3

Information is packed in 8-bit packets (bytes) always followed by an acknowledge bit. The internal data is produced

by sampling sdaat a rising edge of scl The external data must be stable during the high period of scl The exceptions

to this are start(S) or stop (P) conditions when sda falls or rises respectively, while sclis high.

A message contains at least two bytes preceded by a startcondition and followed by either a stopor repeated start,

(Sr), ollowed by another message.

The first byte contains the device address byte which includes the data direction read, r), ~write (~w), bit. The device

address of VV6404 is fixed as 0010_000_[lsb]

2

. The lsb of the address byte indicates the direction of the message.

If the lsb is set high then the master will read data from the slave and if the lsb is reset low then the master will write

data to the slave. After the r,~wbit is sampled, the data direction cannot be changed, until the next address byte with

a new r,~wbit is received.

The byte following the address byte contains the address of the first data byte (also referred to as the index). The

serial interface can address up to 128, byte registers. If the msb of the second byte is set the automatic increment

feature of the address index is selected.

Data Format

1

2

7

8

A

Start condition

Stop condition

SDA

SCL

Acknowledge

P

S

3

4

5

6

Address or data byte

MSB

LSB

Figure 17 : Serial Interface Data Transfer Protocol

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| VV5410 | Mono and Colour Digital Video CMOS Image Sensors |

| VV5430C001 | Monochrome Analog Output CMOS Image Sensors |

| VV5430 | Integrated CMOS Image Sensor with support for ADC and external control via serial interface |

| VV6410C036 | DUAL-MODE DIGITAL CAMERA CHIPSET |

| VV6410 | XTAL MTL T/H HC49/US |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VV5404C001 | 制造商:STMicroelectronics 功能描述:MONO SENSOR - Bulk |

| VV5410 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Mono and Colour Digital Video CMOS Image Sensors |

| VV5410C036 | 制造商:STMicroelectronics 功能描述:IMAGE SENSOR MONOCHROME CMOS 352X288PIXELS 36CLCC - Bulk |

| VV5430 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Integrated CMOS Image Sensor with support for ADC and external control via serial interface |

| VV5430C001 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:Monochrome Analog Output CMOS Image Sensors |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。