- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359351 > VCFOGE NOCKANSCHALTER VARIO 20A PDF資料下載

參數(shù)資料

| 型號: | VCFOGE |

| 英文描述: | NOCKANSCHALTER VARIO 20A |

| 中文描述: | NOCKANSCHALTER巴里奧20A條 |

| 文件頁數(shù): | 1/19頁 |

| 文件大小: | 215K |

| 代理商: | VCFOGE |

W.A.R.P. 1.1

W

EIGHT

A

SSOCIATIVE

R

ULE

P

ROCESSOR

ADVANCED DATA

HighSpeed Rules Processing

AntecedentMembership Functions with any

Shape

Up to 256 Rules (4 Antecedents,1

Consequent)

Up to 16 InputConfigurableVariables

Up to 16 MembershipFunctions foran Input

Variable

Up to 16 OutputVariables

Up to 128 Membership Functions for all

Consequents

MAX-DOT InferenceMethod

Defuzzification on chip

SoftwareTools and Emulators Availability

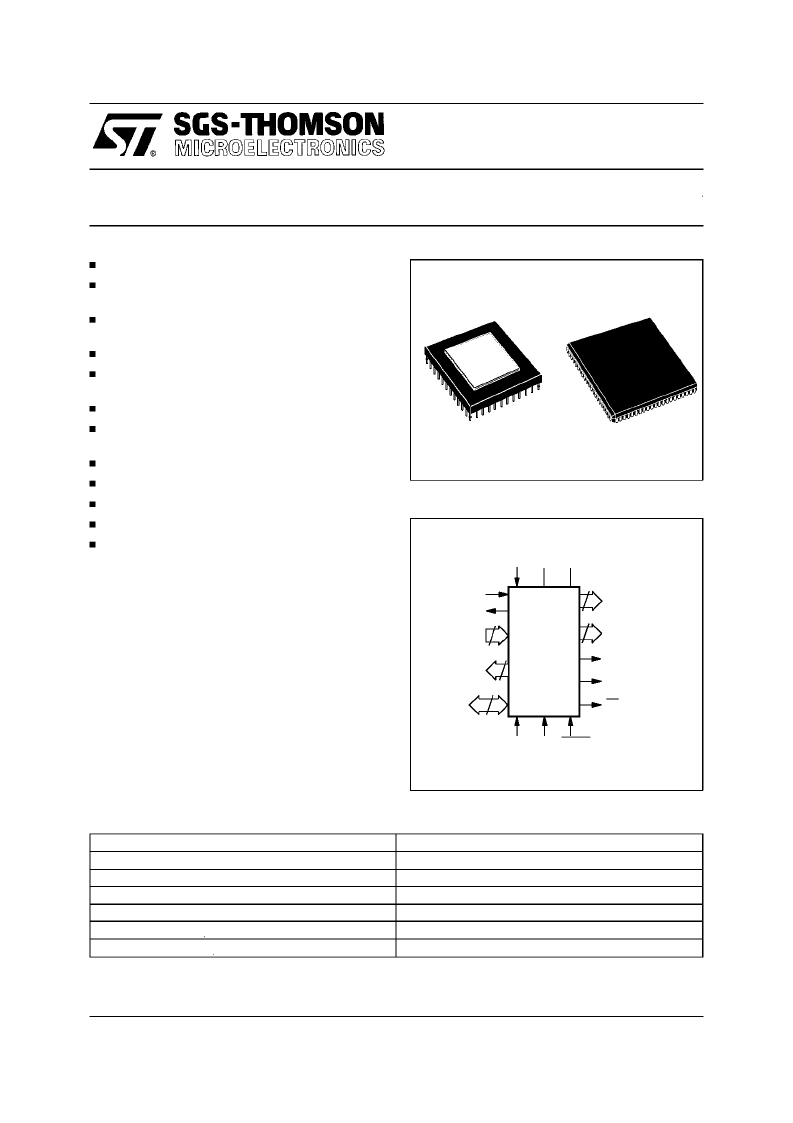

100-pinCPGA100Ceramic Package

84-leadPlastic LeadedChip Carrier package

GENERAL DESCRIPTION

W.A.R.P. is a VLSI Fuzzy Logic controller whose

architecture arises from the need of realizing an

integratedstructure with high inferencingperform-

ancesandflexibility. Toget those resultsa modular

architecture based on a set of parallel memory

blocks has been implemented.

In orderto obtainhighperformancesW.A.R.P.uses

different data representations during the various

phases of the computational cycle, so that it is

always operating on the optimal data repre-

sentation. A vectorial characterization has been

adopted for the Antecedent Membership Func-

tions. W.A.R.P. exploits a SGS-THOMSON pat-

entedstrategytostoretheAntecedentMembership

May 1996

This is advance informationon a new productnow in developmentor undergoingevaluation. Detailsare subject to change without notice.

8

I0-I7

A0-A9

10

O0-O9

FIN

3

CHM OFL

4

OCNT0-OCNT3

STB

EP

NP

PRST

MCLK VSS VDD

W.A.R.P.

1.1

10

EPA0-EPA2

SYNC

Figure1. Logic Diagram

Number of Inputs

Standard Rule Format

Rules Number

Antecedent’s MFs Number

Consequent’s MFs Number

Input Data Resolution

Output Data Resolution

Configurable [1..8]

4 Antecedents, 1 Consequent [or subsets]

Max 256 Rules in the 4Antecedent, 1 Consequent format

Configurable [up to16 for an inputvariable]

Max 256 for all outputs variables

8 bit

8 bit

Table 1. W.A.R.P. Configuration Settings

CPGA100

PLCC84

1/19

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XAPM2203H29 | WIPPSCHALTER ZB2 BOHRUNG 3 |

| XAPM1202H29 | WIPPSCHALTER ZB2 BOHRUNG 2 |

| XAPM1201H29 | WIPPSCHALTER ZB2 BOHRUNG 1 |

| XALJ174 | WIPPSCHALTER ZB2 STEUERGEHAEUSE TASTEN 1 |

| XALB213 | WIPPSCHALTER ZB2 STEUERGEHAEUSE TASTEN 2 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| VCFQ1 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Non Catalogue / VCFQ1 |

| VCFQR1 | 制造商:JOHNSON ELECTRIC 功能描述:SWITCH 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Non Catalogue / VCFQR1 |

| VCFQR2 | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Non Catalogue / VCFQR2 |

| VCFSA1H183JT | 制造商:Panasonic Industrial Company 功能描述:CAPACITOR |

| VCFT | 制造商:SAIA - BURGESS ELECTRONICS INC. 功能描述:Non Catalogue / VCFT |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。