- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359320 > V43658Y04VATG-75PC (Mosel Vitelic, Corp.) 3.3 VOLT 8M x 64 HIGH PERFORMANCE 133 MHZ SDRAM UNBUFFERED SODIMM PDF資料下載

參數(shù)資料

| 型號(hào): | V43658Y04VATG-75PC |

| 廠商: | Mosel Vitelic, Corp. |

| 英文描述: | 3.3 VOLT 8M x 64 HIGH PERFORMANCE 133 MHZ SDRAM UNBUFFERED SODIMM |

| 中文描述: | 3.3伏800萬(wàn)× 64高性能133 MHz的內(nèi)存緩沖的SODIMM |

| 文件頁(yè)數(shù): | 8/11頁(yè) |

| 文件大?。?/td> | 71K |

| 代理商: | V43658Y04VATG-75PC |

8

V43658Y04VATG-75PC Rev. 1.0 July 2001

MOSEL VITELIC

V43658Y04VATG-75PC

Notes:

1.

The specified values are valid when addresses are changed no more than once during t

CK

(min.) and when No

Operation commands are registered on every rising clock edge during t

RC

(min). Values are shown per module

bank.

2.

The specified values are valid when data inputs (DQ

’

s) are stable during t

RC

(min.).

3.

All AC characteristics are shown for device level.

An initial pause of 100

μ

s is required after power-up, then a Precharge All Banks command must be given followed

by 8 Auto Refresh (CBR) cycles before the Mode Register Set Operation can begin.

4.

AC timing tests have V

IL

= 0.4V and V

IH

= 2.4V with the timing referenced to the 1.4V crossover point. The transition

time is measured between V

IH

and V

IL

. All AC measurements assume t

T

= 1 ns with the AC output load circuit

shown. Specific tac and toh parameters are measured with a 50 pF only, without any resistive termination and with

a input signal of 1V / ns edge rate between 0.8V and 2.0V.

5.

If clock rising time is longer than 1 ns, a time (t

T

/2 -0.5) ns has to be added to this parameter.

6.

Rated at 1.5V

7.

If t

T

is longer than 1 ns, a time (t

T

-1) ns has to be added to this parameter.

8.

Any time that the refresh Period has been exceeded, a minimum of two Auto (CBR) Refresh commands must be

given to

“

wake-up

”

the device.

9.

Self Refresh Exit is a synchronous operation and begins on the 2nd positive clock edge after CKE returns high.

Self Refresh Exit is not complete until a time period equal to t

RC

is satisfied once the Self Refresh Exit command

is registered.

10.

Referenced to the time which the output achieves the open circuit condition, not to output voltage levels.

11.

t

DAL

is equivalent to t

DPL

+ t

RP

.

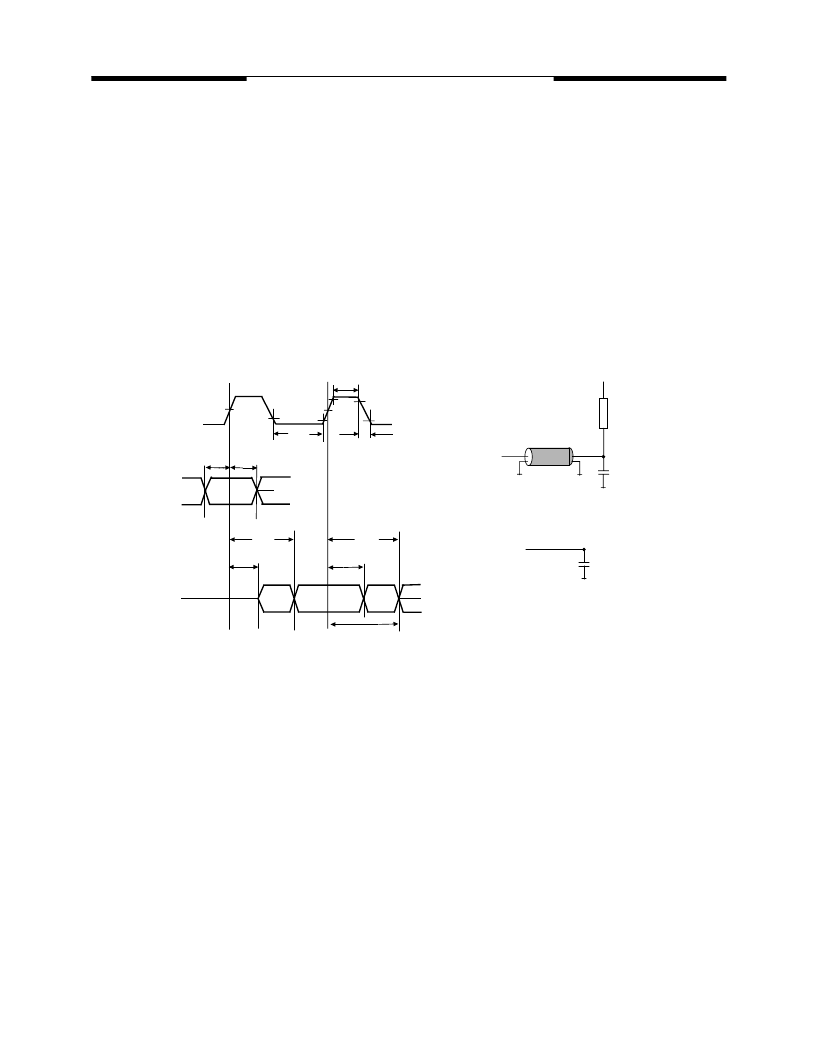

Package Diagram

1.4V

1.4V

tSETUP

tHOLD

tAC

tAC

tLZ

tOH

tHZ

CLOCK

INPUT

OUTPUT

50 pF

I/O

Z=50 Ohm

+ 1.4 V

50 Ohm

2.4V

0.4V

t

T

tCL

tCH

I/O

Measurement conditions for

tac and toh

50 pF

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| V43658Y04VATG-75 | 64MB 168-PIN 133 MHZ SDRAM UNBUFFERED SODIMM 3.3 VOLT, 8M x 64 |

| V436616R24VL | 128 MB 168-PIN UNBUFFERED DIMM 3.3 VOLT 16M x 64 LOW PROFILE |

| V436616R24V | 128 MB 168-PIN UNBUFFERED DIMM 3.3 VOLT 16M x 64 |

| V436616Y24VATG-75PC | 3.3 VOLT 16M x 64 HIGH PERFORMANCE 133 MHZ SDRAM UNBUFFERED SODIMM |

| V436616Y24VATG-75 | 3.3 VOLT 16M x 64 HIGH PERFORMANCE 133 MHZ SDRAM UNBUFFERED SODIMM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| V436616R24V | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128 MB 168-PIN UNBUFFERED DIMM 3.3 VOLT 16M x 64 |

| V436616R24VATG-10PCL | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128 MB 168-PIN UNBUFFERED DIMM 3.3 VOLT 16M x 64 LOW PROFILE |

| V436616R24VATG-75L | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128 MB 168-PIN UNBUFFERED DIMM 3.3 VOLT 16M x 64 LOW PROFILE |

| V436616R24VL | 制造商:MOSEL 制造商全稱:MOSEL 功能描述:128 MB 168-PIN UNBUFFERED DIMM 3.3 VOLT 16M x 64 LOW PROFILE |

| V436616Y04VTG-75 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x64 SDRAM Module |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。