- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376431 > UPD75206CW (NEC Corp.) 4-BIT SINGLE-CHIP MICROCOMPUTER PDF資料下載

參數(shù)資料

| 型號(hào): | UPD75206CW |

| 廠商: | NEC Corp. |

| 英文描述: | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| 中文描述: | 4位單片機(jī) |

| 文件頁數(shù): | 32/62頁 |

| 文件大小: | 489K |

| 代理商: | UPD75206CW |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁當(dāng)前第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

32

μ

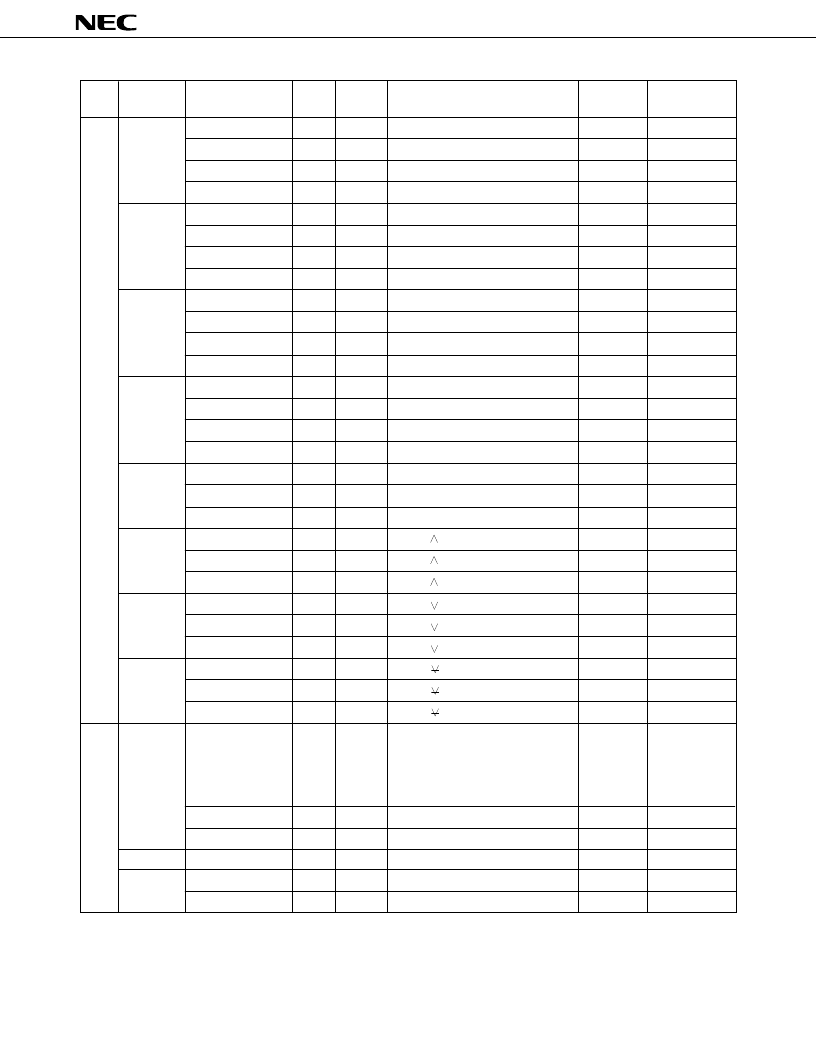

PD75206

mem.bit

2

2

(mem.bit)

←

1

*3

fmem.bit

2

2

(fmem.bit)

←

1

*4

pmem.@L

2

2

(pmem

+L

3–2

.bit(L

1–0

))

←

1

*5

@H + mem.bit

2

2

(H+mem

3–0

.bit)

←

1

*1

mem.bit

2

2

(mem.bit)

←

0

*3

fmem.bit

2

2

(fmem.bit)

←

0

*4

pmem.@L

2

2

(pmem

7–2

+L

3–2

.bit(L

1–0

))

←

0

*5

@H+mem.bit

2

2

(H+mem

3–0

.bit)

←

0

*1

mem.bit

2

2 + S

Skip if (mem.bit) = 1

*3

(mem.bit) = 1

fmem.bit

2

2 + S

Skip if (fmem.bit) = 1

*4

(fmem.bit) = 1

pmem.@L

2

2 + S

Skip if (pmem

7–2

+L

3–2

.bit(L

1–0

)) = 1

*5

(pmem.@L) = 1

@H+mem.bit

2

2 + S

Skip if (H+mem

3–0

.bit) = 1

*1

(@H+mem.bit) = 1

mem.bit

2

2 + S

Skip if (mem.bit) = 0

*3

(mem.bit) = 0

fmem.bit

2

2 + S

Skip if (fmem.bit) = 0

*4

(fmem.bit) = 0

pmem.@L

2

2 + S

Skip if (pmem

7–2

+L

3–2

.bit(L

1–0

)) = 0

*5

(pmem.@L) = 0

@H+mem.bit

2

2 + S

Skip if (H+mem

3–0

.bit) = 0

*1

(@H+mem.bit)= 0

fmem.bit

2

2 + S

Skip if (fmem.bit) = 1 and clear

*4

(fmem.bit) = 1

pmem.@L

2

2 + S

Skip if (pmem

7–2

+L

3–2

.bit(L

1–0

))=1 and clear

*5

(pmem.@L) = 1

@H+mem.bit

2

2 + S

Skip if (H+mem

3–0

.bit)=1 and clear

*1

(@H+mem.bit)=1

CY, fmem.bit

2

2

CY

←

CY

(fmem.bit)

*4

CY, pmem.@L

2

2

CY

←

CY

(pmem

7–2

+L

3–2

.bit(L

1–0

))

*5

CY, @H+mem.bit

2

2

CY

←

CY

(H+mem

3–0

.bit)

*1

CY, fmem.bit

2

2

CY

←

CY

(fmem.bit)

*4

CY, pmem.@L

2

2

CY

←

CY

(pmem

7–2

+L

3–2

.bit(L

1–0

))

*5

CY, @H+mem.bit

2

2

CY

←

CY

(H+mem

3–0

.bit)

*1

CY, fmem.bit

2

2

CY

←

CY

(fmem.bit)

*4

CY, pmem.@L

2

2

CY

←

CY

(pmem

7–2

+L

3–2

.bit(L

1–0

))

*5

CY, @H+mem.bit

2

2

CY

←

CY

(H+mem

3–0

.bit)

*1

addr

—

—

PC

12–0

←

addr

(Optimum instruction is

selected from among BR !addr,

BRCB !caddr and BR $addr by an

assembler.)

PC

12–0

←

addr

*6

!addr

3

3

*6

$addr

1

2

PC

12–0

←

addr

*7

!caddr

2

2

PC

12–0

←

PC

12

+caddr

11–0

*8

PCDE

2

3

PC

12–0

←

PC

12–8

+DE

PCXA

2

3

PC

12–0

←

PC

12–8

+XA

Machine

Cycle

Skip

Condition

Addressing

Area

No. of

Bytes

M

BRCB

B

Note

Instruction Group

Mnemonic

Operands

Operation

Note

SET1

CLR1

SKT

SKF

SKTCLR

AND1

OR1

XOR1

BR

BR

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD75208GF | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208 | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD75208CW | 4-BIT SINGLE-CHIP MICROCOMPUTER |

| UPD753208GT | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD753204 | 4-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD75208 | 制造商:Panasonic Industrial Company 功能描述:IC |

| UPD753012AGC-P33-8BT-A | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD753016AGC-P29-8BT | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD75304GF-407-3B9 | 制造商:Renesas Electronics Corporation 功能描述: |

| UPD75306G182 | 制造商:Panasonic Industrial Company 功能描述:IC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。