- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄378744 > UPD703033AGF (NEC Corp.) V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS PDF資料下載

參數(shù)資料

| 型號: | UPD703033AGF |

| 廠商: | NEC Corp. |

| 英文描述: | V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| 中文描述: | V850/SB1TM 32-/16-BIT單晶片微控制器 |

| 文件頁數(shù): | 44/56頁 |

| 文件大小: | 357K |

| 代理商: | UPD703033AGF |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁當(dāng)前第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁

Data Sheet U14734EJ1V0DS00

44

μ

PD703031A, 703031AY, 703033A, 703033AY, 70F3033A, 70F3033AY

(10)I

2

C bus mode (

μ

PD703031AY, 703033AY, 70F3033AY only)

(T

A

= –40 to +85°C, V

DD

= 4.0 to 5.5 V, EV

DD

= 3.0 to 5.5 V, V

SS

= EV

SS

= 0 V)

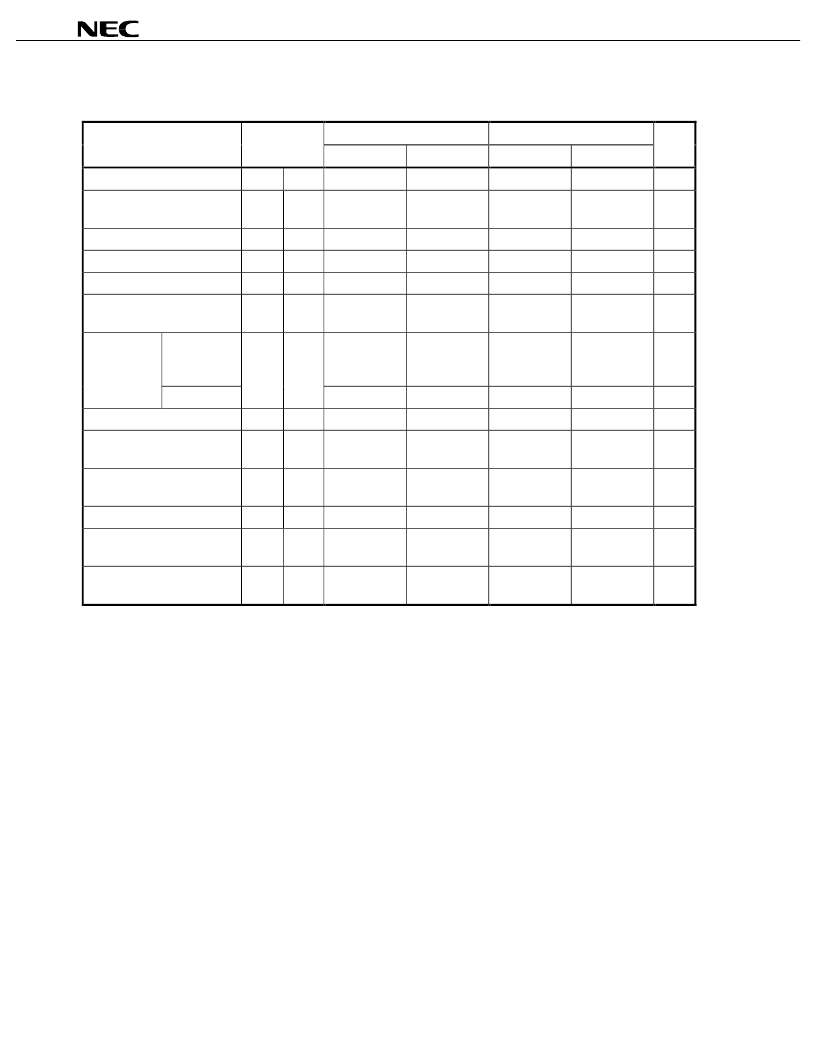

Normal Mode

High-Speed Mode

Parameter

Symbol

MIN.

MAX.

MIN.

MAX.

Unit

SCLn clock frequency

–

f

CLK

0

100

0

400

kHz

Bus-free time (between

stop/start conditions)

<74>

t

BUF

4.7

–

1.3

–

μ

s

Hold time

Note 1

<75>

t

HD:STA

4.0

–

0.6

–

μ

s

SCLn clock low-level width

<76>

t

LOW

4.7

–

1.3

–

μ

s

SCLn clock high-level width

<77>

t

HIGH

4.0

–

0.6

–

μ

s

Setup time for start/restart

conditions

<78>

t

SU:STA

4.7

–

0.6

–

μ

s

CBUS

compatible

master

5.0

–

–

–

μ

s

Data hold

time

I

2

C mode

<79>

t

HD:DAT

0

Note 2

–

0

Note 2

0.9

Note 3

μ

s

Data setup time

<80>

t

SU:DAT

250

–

100

Note 4

–

ns

SDAn and SCLn signal rise

time

<81>

t

R

–

1000

20 + 0.1Cb

Note 5

300

ns

SDAn and SCLn signal fall

time

<82>

t

F

–

300

20 + 0.1Cb

Note 5

300

ns

Stop condition setup time

<83>

t

SU:STO

4.0

–

0.6

–

μ

s

Pulse width of spike

suppressed by input filter

<84>

t

SP

–

–

0

50

ns

Capacitance load of each

bus line

–

Cb

–

400

–

400

pF

Notes 1.

At the start condition, the first clock pulse is generated after the hold time.

2.

The system requires a minimum of 300 ns hold time internally for the SDAn signal (at V

IHmin.

.

of SCLn

signal) in order to occupy the undefined area at the falling edge of SCLn.

3.

If the system does not extend the SCLn signal low hold time (t

LOW

), only the maximum data hold time

(t

HD

:

DAT

) needs to be satisfied.

4.

The high-speed mode I

high-speed mode I

If the system does not extend the SCLn signal’s low state hold time:

t

HD

:

DAT

≥

250 ns

If the system extends the SCLn signal’s low state hold time:

Transmit the following data bit to the SDAn line prior to the SCLn line release (t

Rmax.

+ t

SU

:

DAT

= 1000

+ 250 = 1250 ns: Normal mode I

5.

Cb: Total capacitance of one bus line (unit: pF)

2

C bus can be used in the normal-mode I

2

C bus system. In this case, set the

2

C bus so that it meets the following conditions.

2

C bus specification).

Remark

n = 0, 1

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| UPD703033AY | V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD70F3033AYGC-8EU | Circular Connector; MIL SPEC:MIL-C-5015 E/F/R; Body Material:Aluminum Alloy; Series:MS3106; No. of Contacts:3; Connector Shell Size:10SL; Connecting Termination:Solder; Circular Shell Style:Straight Plug; Gender:Female RoHS Compliant: No |

| UPD703031AYGF | V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703033AYGF | V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD70F3033AYGF-3BA | V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| UPD703033AY | 制造商:NEC 制造商全稱:NEC 功能描述:V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703033AYGC | 制造商:NEC 制造商全稱:NEC 功能描述:V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703033AYGF | 制造商:NEC 制造商全稱:NEC 功能描述:V850/SB1TM 32-/16-BIT SINGLE-CHIP MICROCONTROLLERS |

| UPD703033B | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:V850/SB1(TM).V850/SB2(TM) for Hardware | UM Including Electrical Characteristics[02/2003] |

| UPD703033BY | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:V850 Series Pamphlet | Pamphlet[02/2002] |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。