- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄382707 > U631H64DK35 NVRAM (EEPROM Based) PDF資料下載

參數(shù)資料

| 型號(hào): | U631H64DK35 |

| 英文描述: | NVRAM (EEPROM Based) |

| 中文描述: | NVRAM中(EEPROM的基礎(chǔ)) |

| 文件頁(yè)數(shù): | 8/12頁(yè) |

| 文件大小: | 125K |

| 代理商: | U631H64DK35 |

8

November 01, 2001

U631H64

n:

o:

p:

q:

The software sequence is clocked with E controlled READs.

Once the software controlled STORE or RECALL cycle is initiated, it completes automatically, ignoring all inputs.

Note that STORE cycles (but not RECALL) are aborted by V

CC

< V

SWITCH

(STORE inhibit).

An automatic RECALL also takes place at power up, starting when V

CC

exceeds V

SWITCH

and takes t

RESTORE

. V

CC

must not drop below

V

once it has been exceeded for the RECALL to function properly.

Noise on the E pin may trigger multiple READ cycles from the same address and abort the address sequence.

If the Chip Enable Pulse Width is less than t

a(E)

(see Read Cycle) but greater than or equal t

w(E)SR

, than the data may not be valid at

the end of the low pulse, however the STORE or RECALL will still be initiated.

r:

s:

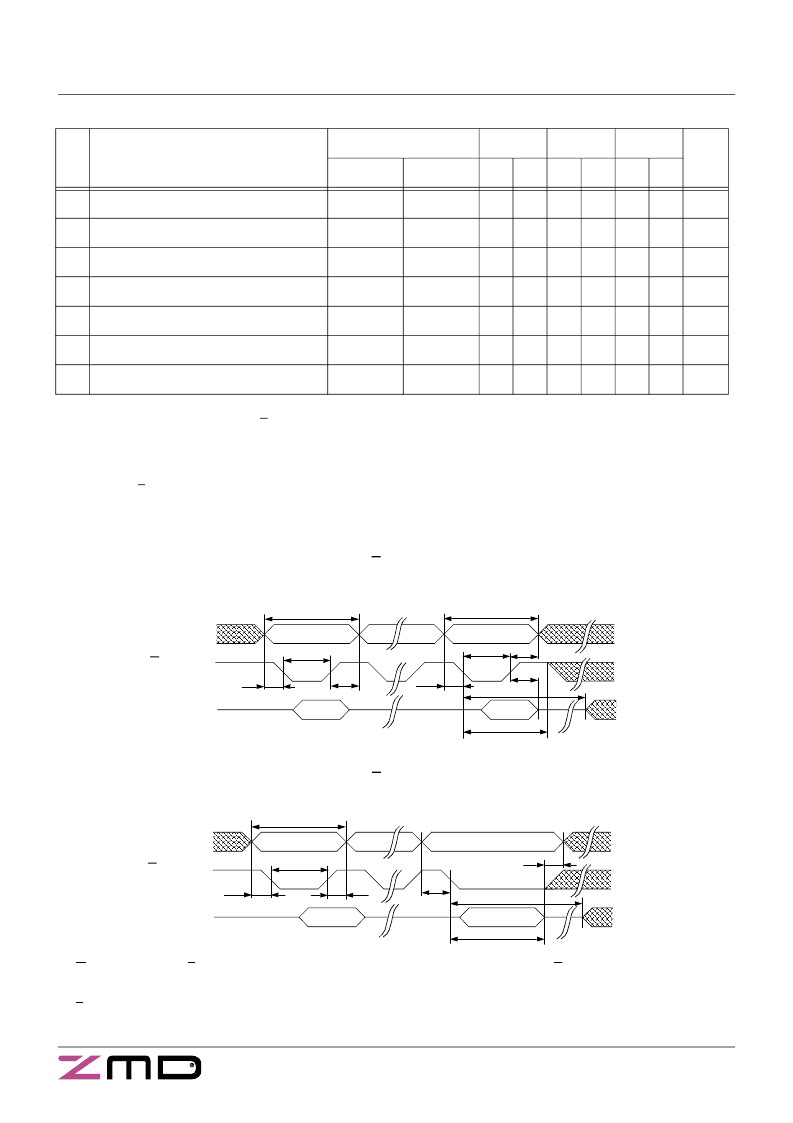

No. Software Controlled STORE/RECALL

Cycle

l, n

Symbol

25

35

45

Unit

Alt.

IEC

Min. Max. Min. Max. Min. Max.

25 STORE/RECALL Initiation Time

t

AVAV

t

cR

25

35

45

ns

26 Chip Enable to Output Inactive

o

t

ELQZ

t

dis(E)SR

600

600

600

ns

27 STORE Cycle Time

p

t

ELQXS

t

d(E)S

10

10

10

ms

28 RECALL Cycle Time

q

t

ELQXR

t

d(E)R

20

20

20

μ

s

29 Address Setup to Chip Enable

r

t

AVELN

t

su(A)SR

0

0

0

ns

30 Chip Enable Pulse Width

r, s

t

ELEHN

t

w(E)SR

20

25

35

ns

31 Chip Disable to Address Change

r

t

EHAXN

t

h(A)SR

0

0

0

ns

Ai

E

DQi

Output

t

cR

t

w(E)SR

(30)

High Impedance

ADDRESS 1

VALID

VALID

Software Controlled STORE/RECALL Cycle

r, s, t, u

(E = HIGH after STORE initiation)

ADDRESS 6

t

w(E)SR

(30)

t

cR

(25)

(25)

t

h(A)SR

(31)

t

su(A)SR

Ai

E

DQi

Output

t

cR

t

w(E)SR

(30)

High Impedance

ADDRESS 1

VALID

VALID

t

dis(E)SR

(26)

ADDRESS 6

t

d(E)S

(27)

(28)

(25)

t

h(A)SR

(31)

t

su(A)SR

(29)

t

h(A)SR

(31)

t

su(A)SR

(29)

t

h(A)SR

(31)

t

su(A)SR

(29)

(5)

t

dis(E)

t

d(E)R

Software Controlled STORE/RECALL Cycle

r, s, t, u

(E = LOW after STORE initiation)

t

dis(E)SR

(26)

(29)

t

d(E)S

(27)

(28)

t

d(E)R

t:

W must be HIGH when E is LOW during the address sequence in order to initiate a nonvolatile cycle. G may be either HIGH or LOW

throughout. Addresses 1 through 6 are found in the mode selection table. Address 6 determines whether the U631H64 performs a STORE

or RECALL.

E must be used to clock in the address sequence for the Software controlled STORE and RECALL cycles.

u:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| U631H64DK45 | Low power single operational amplifier |

| U631H64SC25 | NVRAM (EEPROM Based) |

| U631H64SC35 | NVRAM (EEPROM Based) |

| U631H64SC45 | NVRAM (EEPROM Based) |

| U631H64SK25 | High performance quad bipolar operational amplifier |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| U631H64DK35G1 | 制造商:SIMTEK 制造商全稱(chēng):Simtek Corporation 功能描述:SoftStore 8K x 8 nvSRAM |

| U631H64DK45 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:NVRAM (EEPROM Based) |

| U631H64DK45G1 | 制造商:SIMTEK 制造商全稱(chēng):Simtek Corporation 功能描述:SoftStore 8K x 8 nvSRAM |

| U631H64S2C25 | 制造商:SIMTEK 制造商全稱(chēng):Simtek Corporation 功能描述:SoftStore 8K x 8 nvSRAM |

| U631H64S2C25G1 | 制造商:SIMTEK 制造商全稱(chēng):Simtek Corporation 功能描述:SoftStore 8K x 8 nvSRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。