- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371188 > TSC2200 PDA ANALOG INTERFACE CIRCUIT PDF資料下載

參數(shù)資料

| 型號: | TSC2200 |

| 英文描述: | PDA ANALOG INTERFACE CIRCUIT |

| 中文描述: | 掌上電腦模擬接口電路 |

| 文件頁數(shù): | 16/40頁 |

| 文件大小: | 645K |

| 代理商: | TSC2200 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

16

www.ti.com

TSC2200

SBAS191F

AV1

AV0

FUNCTION

0

0

1

1

0

1

0

1

None

4 Data Averages

8 Data Averages

16 Data Averages

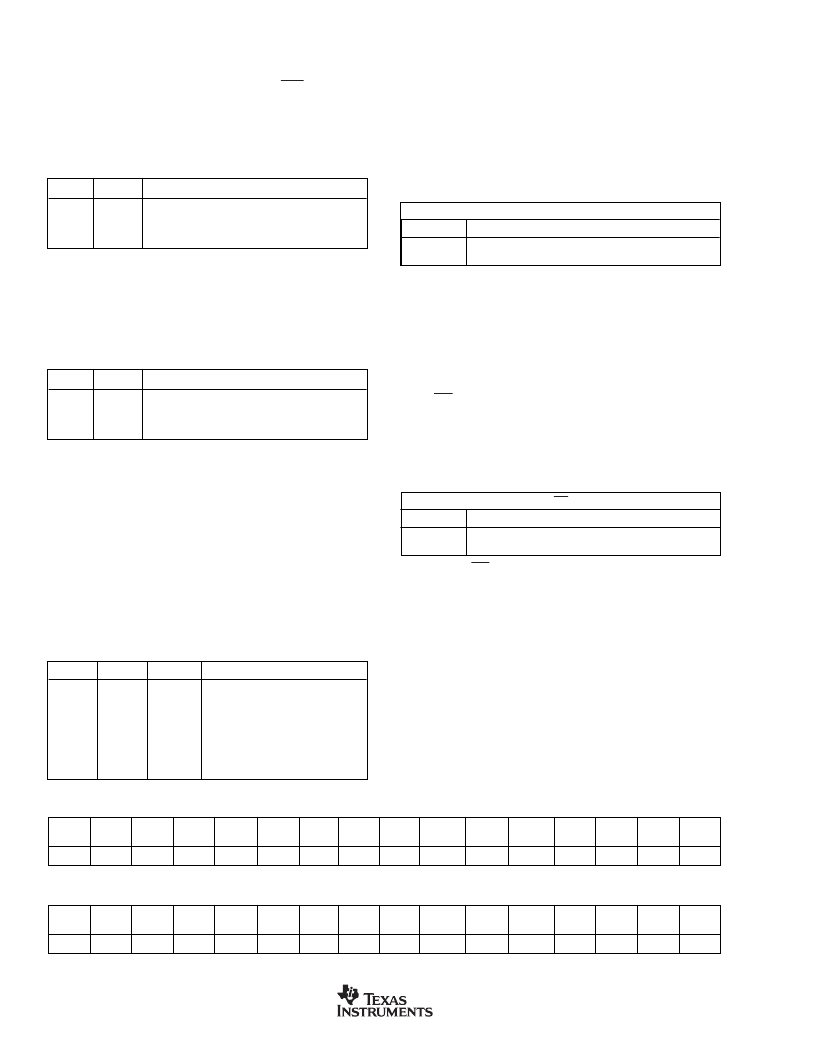

TABLE X. A/D Conversion Averaging Control.

CL1

CL0

FUNCTION

0

0

1

1

0

1

0

1

8MHz Internal Clock Rate

—

8-Bit Resolution Only

4MHz Internal Clock Rate

—

10-Bit Resolution Only

2MHz Internal Clock Rate

1MHz Internal Clock Rate

TABLE XI. A/D Converter Clock Control.

MSB

BIT 15

LSB

BIT 0

BIT 14

BIT 13

BIT 12

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

DPD

X

X

X

X

X

X

X

X

X

X

X

X

X

X

X

TABLE XIII. D/A Converter Control Register.

MSB

BIT 15

LSB

BIT 0

BIT 14

BIT 13

BIT 12

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

X

X

X

X

X

X

X

X

X

X

X

INT

DL1

DL0

PDN

RFV

TABLE XV. Reference Register.

PV2

PV1

PV0

FUNCTION

0

μ

s

Stabilization Time

100

μ

s

Stabilization Time

500

μ

s

Stabilization Time

1ms Stabilization Time

5ms Stabilization Time

10ms Stabilization Time

50ms Stabilization Time

100ms Stabilization Time

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

TABLE XII. Panel Voltage Stabilization Time Control.

DPD

VALUE

DESCRIPTION

0

1

D/A Converter is Powered and Operational

D/A Converter is Powered Down

TABLE XIV. DPD Bit Operation.

INT

VALUE

DESCRIPTION

0

1

External Reference Selected

Internal Reference Selected

TABLE XVI.

INT

Bit Operation.

Bits[7:6]: AV1, AV0

—

Converter Averaging Control. These

two bits allow you to specify the number of averages the

converter will perform, as shown in Table X. Note that when

averaging is used, the STS bit and the

DAV

output will

indicate that the converter is busy until all conversions

necessary for the averaging are complete. The default state

for these bits is 00, selecting no averaging. These bits are the

same whether reading or writing.

Bits[5:4]: CL1, CL0

—

Conversion Clock Control. These two

bits specify the internal clock rate which the A/D converter uses

when performing a single conversion, as shown in Table XI.

These bits are the same whether reading or writing.

Bits [3:1]: PV2

–

PV0

—

Panel Voltage Stabilization Time

control. These bits allow you to specify a delay time from the

time a pen touch is detected to the time a conversion is

started. This allows you to select the appropriate settling time

for the touch panel used. Table XII shows the settings of

these bits. The default state is 000, indicating a 0ms stabili-

zation time. These bits are the same whether reading or

writing.

Bit 0:

This bit is not used, and is a

“

don

’

t care

”

when writing.

It will always read as a zero.

D/A CONVERTER CONTROL REGISTER

(PAGE 1, ADDRESS 02

H

)

The single bit in this register controls the power down control

of the onboard D/A converter. This register is formatted as

shown in Table XIII.

Bit 15: DPD

—

D/A Converter Power Down. This bit controls

whether the D/A converter is powered up and operational, or

powered down. If the D/A converter is powered down, the

A

OUT

pin will neither sink nor source current.

REFERENCE REGISTER

(PAGE 1, ADDRESS 03

H

)

The TSC2200 has a register to control the operation of the

internal reference. This register is formatted as shown in

Table XV.

Bit 4:

INT

—

Internal Reference Mode. If this bit is written to a

1, the TSC2200 will use its internal reference; if this bit is a

zero, the part will assume an external reference is being

supplied. The default state for this bit is to select an external

reference (0). This bit is the same whether reading or writing.

Bits [3:2]: DL1, DL0

—

Reference Power-Up Delay. When

the internal reference is powered up, a finite amount of time

is required for the reference to settle. If measurements are

made before the reference has settled, these measurements

will be in error. These bits allow for a delay time for measure-

ments to be made after the reference powers up, thereby

assuring that the reference has settled. Longer delays will be

necessary depending upon the capacitance present at the

REF pin (see Typical Characteristics).

See Table XVII for the delays. The default state for these bits

is 00, selecting a 0

μ

s delay. These bits are the same whether

reading or writing.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TSC2200IPW | PDA ANALOG INTERFACE CIRCUIT |

| TSC2200IPWR | PDA ANALOG INTERFACE CIRCUIT |

| TSC2200IRHB | PDA ANALOG INTERFACE CIRCUIT |

| TSC2200IRHBR | PDA ANALOG INTERFACE CIRCUIT |

| TSC83251G2D | 0.5 Um SCMOS3 Technology |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TSC2200EVM | 功能描述:觸摸傳感器開發(fā)工具 Touch Screen Contr Eval Mod RoHS:否 制造商:Cypress Semiconductor 工具用于評估: 接口類型: 工作電壓: 最大工作溫度: |

| TSC2200IPW | 功能描述:觸摸屏轉(zhuǎn)換器和控制器 Prog 4-Wire w/12-Bit 125KHz ADC & Key Ifc RoHS:否 制造商:Microchip Technology 類型:Resistive Touch Controllers 輸入類型:3 Key 數(shù)據(jù)速率:140 SPS 分辨率:10 bit 接口類型:4-Wire, 5-Wire, 8-Wire, I2C, SPI 電源電壓:2.5 V to 5.25 V 電源電流:17 mA 工作溫度:- 40 C to + 85 C 封裝 / 箱體:SSOP-20 |

| TSC2200IPWG4 | 功能描述:觸摸屏轉(zhuǎn)換器和控制器 Prog 4-Wire w/12-Bit 125KHz ADC & Key Ifc RoHS:否 制造商:Microchip Technology 類型:Resistive Touch Controllers 輸入類型:3 Key 數(shù)據(jù)速率:140 SPS 分辨率:10 bit 接口類型:4-Wire, 5-Wire, 8-Wire, I2C, SPI 電源電壓:2.5 V to 5.25 V 電源電流:17 mA 工作溫度:- 40 C to + 85 C 封裝 / 箱體:SSOP-20 |

| TSC2200IPWR | 功能描述:觸摸屏轉(zhuǎn)換器和控制器 Prog 4-Wire w/12-Bit 125KHz ADC & Key Ifc RoHS:否 制造商:Microchip Technology 類型:Resistive Touch Controllers 輸入類型:3 Key 數(shù)據(jù)速率:140 SPS 分辨率:10 bit 接口類型:4-Wire, 5-Wire, 8-Wire, I2C, SPI 電源電壓:2.5 V to 5.25 V 電源電流:17 mA 工作溫度:- 40 C to + 85 C 封裝 / 箱體:SSOP-20 |

| TSC2200IPWRG4 | 功能描述:觸摸屏轉(zhuǎn)換器和控制器 Prog 4-Wire w/12-Bit 125KHz ADC & Key Ifc RoHS:否 制造商:Microchip Technology 類型:Resistive Touch Controllers 輸入類型:3 Key 數(shù)據(jù)速率:140 SPS 分辨率:10 bit 接口類型:4-Wire, 5-Wire, 8-Wire, I2C, SPI 電源電壓:2.5 V to 5.25 V 電源電流:17 mA 工作溫度:- 40 C to + 85 C 封裝 / 箱體:SSOP-20 |

發(fā)布緊急采購,3分鐘左右您將得到回復。