- 您現(xiàn)在的位置:買賣IC網 > PDF目錄272329 > TS80C51RA2-VLBB (ATMEL CORP) 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號: | TS80C51RA2-VLBB |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 40 MHz, MICROCONTROLLER, PQCC44 |

| 封裝: | PLASTIC, LCC-44 |

| 文件頁數(shù): | 20/83頁 |

| 文件大?。?/td> | 8336K |

| 代理商: | TS80C51RA2-VLBB |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

195

7679H–CAN–08/08

AT90CAN32/64/128

17.11 USART Register Description

17.11.1

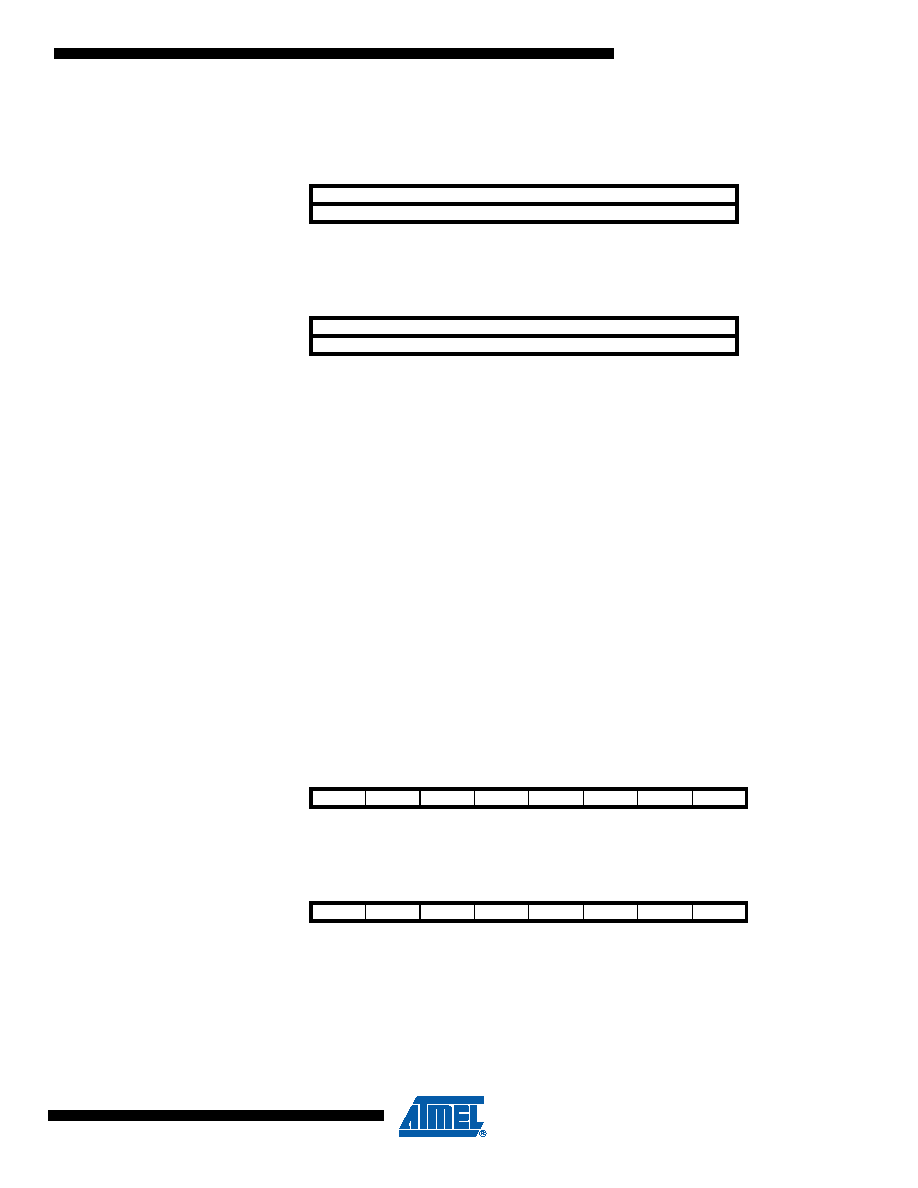

USART0 I/O Data Register – UDR0

17.11.2

USART1 I/O Data Register – UDR1

Bit 7:0 – RxBn7:0: Receive Data Buffer (read access)

Bit 7:0 – TxBn7:0: Transmit Data Buffer (write access)

The USARTn Transmit Data Buffer Register and USARTn Receive Data Buffer Registers share

the same I/O address referred to as USARTn Data Register or UDRn. The Transmit Data Buffer

Register (TXBn) will be the destination for data written to the UDRn Register location. Reading

the UDRn Register location will return the contents of the Receive Data Buffer Register (RXBn).

For 5-, 6-, or 7-bit characters the upper unused bits will be ignored by the Transmitter and set to

zero by the Receiver.

The transmit buffer can only be written when the UDREn flag in the UCSRnA Register is set.

Data written to UDRn when the UDREn flag is not set, will be ignored by the USARTn Transmit-

ter. When data is written to the transmit buffer, and the Transmitter is enabled, the Transmitter

will load the data into the Transmit Shift Register when the Shift Register is empty. Then the

data will be serially transmitted on the TxDn pin.

The receive buffer consists of a two level FIFO. The FIFO will change its state whenever the

receive buffer is accessed.

17.11.3

USART0 Control and Status Register A – UCSR0A

17.11.4

USART1 Control and Status Register A – UCSR1A

Bit 7 – RXCn: USARTn Receive Complete

This flag bit is set when there are unread data in the receive buffer and cleared when the receive

buffer is empty (i.e., does not contain any unread data). If the Receiver is disabled, the receive

buffer will be flushed and consequently the RXCn bit will become zero. The RXCn flag can be

used to generate a Receive Complete interrupt (see description of the RXCIEn bit).

Bit

7

6

543

210

RXB0[7:0]

UDR0 (Read)

TXB0[7:0]

UDR0 (Write)

Read/Write

R/W

Initial Value

0

Bit

7

6

543

210

RXB1[7:0]

UDR1 (Read)

TXB1[7:0]

UDR1 (Write)

Read/Write

R/W

Initial Value

0

Bit

765

4321

0

RXC0

TXC0

UDRE0

FE0

DOR0

UPE0

U2X0

MPCM0

UCSR0A

Read/Write

R

R/W

R

R/W

Initial Value

001

0000

0

Bit

765

4321

0

RXC1

TXC1

UDRE1

FE1

DOR1

UPE1

U2X1

MPCM1

UCSR1A

Read/Write

R

R/W

R

R/W

Initial Value

001

0000

0

相關PDF資料 |

PDF描述 |

|---|---|

| TS87C52X2-VLEB | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP44 |

| TS87C54X2-VLBB | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQCC44 |

| TSC80C31-12KA | 8-BIT, 12 MHz, MICROCONTROLLER, PDIP40 |

| TS80C52X2ZZZ-LIE | 8-BIT, MROM, 30 MHz, MICROCONTROLLER, PQFP44 |

| TS87C52X2-MIE | 8-BIT, OTPROM, 40 MHz, MICROCONTROLLER, PQFP44 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TS80C51RB2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TS87C51RB2. TS80C51RB2 Errata [Updated 4/03. 3 Pages] |

| TS80C51RC2 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:TS87C51RC2. TS80C51RC2 Errata [Updated . Pages] |

| TS80C51RD2 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:High Performance 8-bit Microcontrollers |

| TS80C51RD2-EAD | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

| TS80C51RD2-EBB | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Microcontroller |

發(fā)布緊急采購,3分鐘左右您將得到回復。