- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄361519 > TP82510 (Innovasic Semiconductor) CONNECTOR ACCESSORY PDF資料下載

參數(shù)資料

| 型號: | TP82510 |

| 廠商: | Innovasic Semiconductor |

| 英文描述: | CONNECTOR ACCESSORY |

| 中文描述: | 異步串行控制器 |

| 文件頁數(shù): | 7/14頁 |

| 文件大?。?/td> | 76K |

| 代理商: | TP82510 |

IA82510

ASYNCHRONOUS SERIAL CONTROLLER

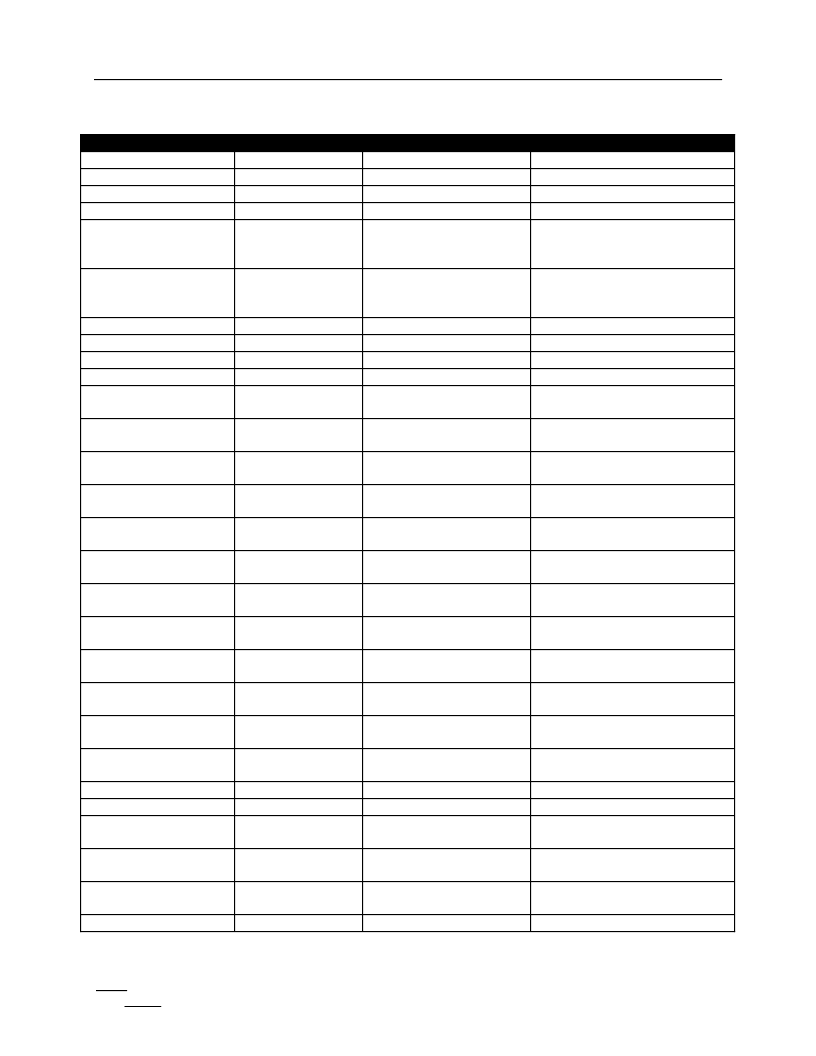

AC Characteristics

Parameter

Min

CLK period

54 ns

CLK period

54 ns

CLK Low Time

25 ns

CLK High Time

25 ns

Data Sheet

As of Production Ver. 01

Copyright

2001

innov

ASIC

The End of Obsolescence

ENG211001219-01

www.innovasic.com

Customer Support:

Page 7 of 14

1-888-824-4184

Max

Notes

250 ns

108 ns

10 ns

Divide by Two

No Divide by

Divide by Two

Measured between 0.3 * VDD

and 0.7 * VDD

Divide by Two

Measured between 0.3 * VDD

and 0.7 * VDD

No Divide by

No Divide by

CLK Rise Time

CLK Fall Time

CLK Rise Time

CLK Fall Time

Crystal Frequency

Reset Width

RTS/DTR Low Setup

to Reset inactive

RTS/DTR Low Hold

after Reset inactive

10 ns

1 Mhz

8 * Clock Period

6 * Clock Period

15 ns

15 ns

20 Mhz

Clock Period – 20 ns

RDn Active Width

Address/CSn Setup

Time to RDn Active

Address/CSn Hold

after RDn Inactive

RDn or WRn Inactive

to Active Delay

Data Out Float Delay

after RDn Inactive

2* clock period +

65 ns

7 ns

0 ns

Clock Period +

15 ns

40 ns

WRn Active Width

Address CSn Setup

Time to WRn Active

Address and CSn

hold Time after WRn

Data in Setup Time

to WRn Inactive

Data In Hold Time

after WRn Inactive

SCLK Period

SCLK Period

RXD Setup Time to

SCLK High

RXD Hold Time after

SCLK High

TXD Valid after SCLK

Low

TXD Delay after RXD

2 * Clock Period

+ 15 ns

7 ns

0 ns

90 ns

12 ns

216 ns

3500 ns

250 ns

16x Clocking Mode

1x Clocking Mode

250 ns

170 ns

170 ns

Remote Loopback

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPL10115 | CONNECTOR ACCESSORY |

| TPL10105 | CONNECTOR ACCESSORY |

| TPL10112 | CONNECTOR ACCESSORY |

| TPL10124 | CONNECTOR ACCESSORY |

| TPL10212 | CONNECTOR ACCESSORY |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TP82530-6 | 制造商:Rochester Electronics LLC 功能描述: |

| TP8256AH | 制造商:Rochester Electronics LLC 功能描述: |

| TP8289-1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:80x86 Bus Arbiter |

| TP82C54 | 制造商:Rochester Electronics LLC 功能描述: |

| TP82C54-2 | 制造商:Rochester Electronics LLC 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。