- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359296 > TMS320VC5421PGE (Texas Instruments, Inc.) DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320VC5421PGE |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 110/123頁(yè) |

| 文件大小: | 1205K |

| 代理商: | TMS320VC5421PGE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)當(dāng)前第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

www.ti.com

6.9.7.1

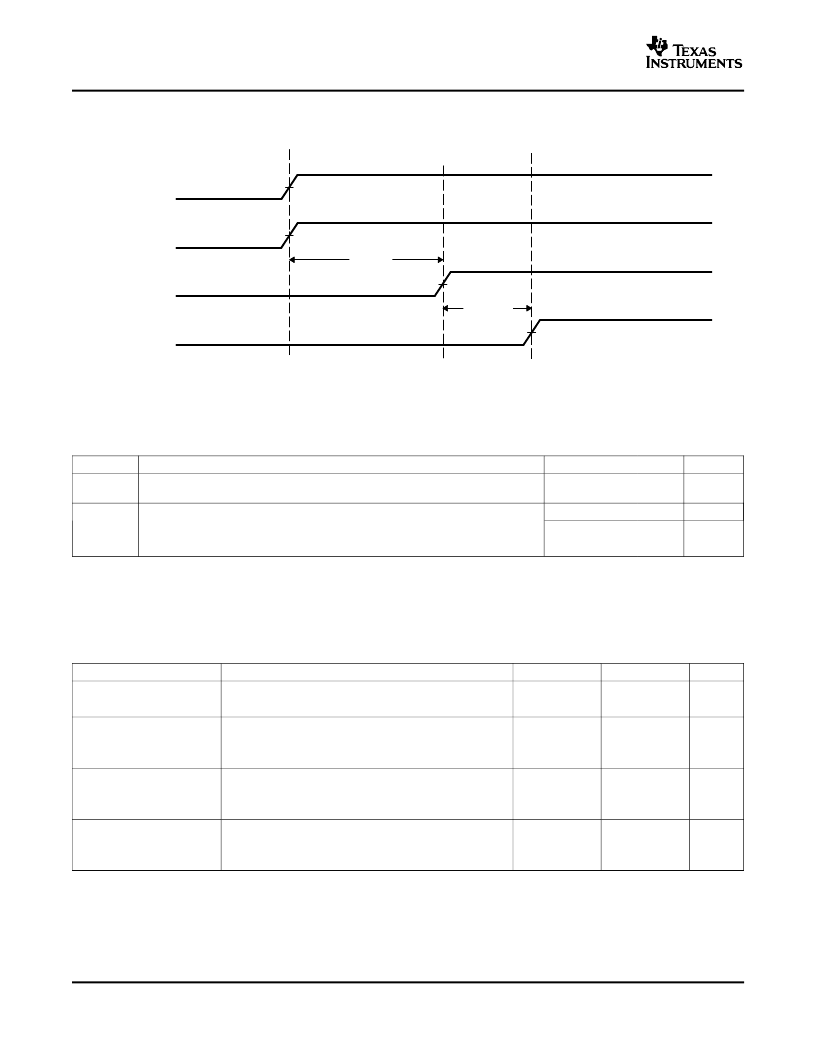

ADC Power-Up Control Bit Timing

ADC Power Up Delay

ADC Ready for Conversions

PWDNBG

PWDNREF

PWDNADC

Request for

ADC

Conversion

t

d(BGR)

t

d(PWD)

TMS320F2808, TMS320F2806

TMS320F2801, UCD9501

Digital Signal Processors

SPRS230F–OCTOBER 2003–REVISED SEPTEMBER 2005

Figure 6-21. ADC Power-Up Control Bit Timing

Table 6-37. ADC Power-Up Delays

PARAMETER

(1)

Delay time for band gap reference to be stable. Bits 7 and 6 of the ADCTRL3

register (ADCBGRFDN1/0) must be set to 1 before the PWDNADC bit is enabled.

Delay time for power-down control to be stable. Bit delay time for band-gap

reference to be stable. Bits 7 and 6 of the ADCTRL3 register (ADCBGRFDN1/0)

must be set to 1 before the PWDNADC bit is enabled. Bit 5 of the ADCTRL3

register (PWDNADC)must be set to 1 before any ADC conversions are initiated.

MIN

TYP

5

MAX

UNIT

ms

t

d(BGR)

t

d(PWD)

20

50

μ

s

ms

1

(1)

Timings maintain compatibility to the 281x ADC module. The 280x ADC also supports driving all 3 bits at the same time and waiting

t

d(BGR)

ms before first conversion.

Table 6-38. Current Consumption for Different ADC Configurations (at 12.5-MHz ADCCLK)

(1)(2)

ADC OPERATING MODE

Mode A (Operational Mode):

CONDITIONS

V

DDA18

30

V

DDA3.3

2

UNIT

mA

BG and REF enabled

PWD disabled

Mode B:

9

0.5

ma

ADC clock enabled

BG and REF enabled

PWD enabled

Mode C:

5

20

μ

A

ADC clock enabled

BG and REF disabled

PWD enabled

Mode D:

5

15

μ

A

ADC clock disabled

BG and REF disabled

PWD enabled

(1)

Test Conditions:

SYSCLKOUT = 100 MHz

ADC module clock = 12.5 MHz

ADC performing a continuous conversion of all 16 channels in Mode A

V

DDA18

includes current into V

DD1A18

and V

DD2A18

. V

DDA3.3

includes current into V

DDA2

and V

DDAIO

.

(2)

110

Electrical Specifications

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320F241PGE | DSP CONTROLLERS |

| TMS320C6211PZ150 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMS320C6211PZ120 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMS320C6211PZ100 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMS320C6211JDA167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320VC5421PGE200 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320VC5421ZGU200 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Dig Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320VC5441AGGU | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320VC5441APGF | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Dig Signal Processor RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320VC5441AZGU | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Fixed-Point Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。