- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359301 > TMS320VC33PGE (Texas Instruments, Inc.) DIGITAL SIGNAL PROCESSOR PDF資料下載

參數(shù)資料

| 型號(hào): | TMS320VC33PGE |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 數(shù)字信號(hào)處理 |

| 英文描述: | DIGITAL SIGNAL PROCESSOR |

| 中文描述: | 數(shù)字信號(hào)處理器 |

| 文件頁(yè)數(shù): | 44/123頁(yè) |

| 文件大?。?/td> | 1205K |

| 代理商: | TMS320VC33PGE |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)第101頁(yè)第102頁(yè)第103頁(yè)第104頁(yè)第105頁(yè)第106頁(yè)第107頁(yè)第108頁(yè)第109頁(yè)第110頁(yè)第111頁(yè)第112頁(yè)第113頁(yè)第114頁(yè)第115頁(yè)第116頁(yè)第117頁(yè)第118頁(yè)第119頁(yè)第120頁(yè)第121頁(yè)第122頁(yè)第123頁(yè)

www.ti.com

3.6.2

Watchdog Block

/512

OSCCLK

WDCR (WDPS(2:0))

WDCLK

WDCNTR(7:0)

WDKEY(7:0)

Bad Key

Good Key

1

0

1

WDCR (WDCHK(2:0))

Bad

WDCHK

Key

WDCR (WDDIS)

Clear Counter

SCSR (WDENINT)

Watchdog

Prescaler

Generate

Output Pulse

(512 OSCCLKs)

8-Bit

Watchdog

Counter

CLR

WDRST

WDINT

Watchdog

55 + AA

Key Detector

XRS

Core-reset

WDRST

(A)

Internal

Pullup

TMS320F2808, TMS320F2806

TMS320F2801, UCD9501

Digital Signal Processors

SPRS230F–OCTOBER 2003–REVISED SEPTEMBER 2005

Normally, when the input clocks are present, the watchdog counter decrements to initiate a watchdog

reset or WDINT interrupt. However, when the external input clock fails, the watchdog counter stops

decrementing (i.e., the watchdog counter does not change with the limp-mode clock). In addition to this,

the device will be reset and the “Missing Clock Status” (MCLKSTS) bit will be set. These conditions could

be used by the application firmware to detect the input clock failure and initiate necessary shut-down

procedure for the system.

NOTE

Applications in which the correct CPU operating frequency is absolutely critical should

implement a mechanism by which the DSP will be held in reset, should the input clocks

ever fail. For example, an R-C circuit may be used to trigger the XRS pin of the DSP,

should the capacitor ever get fully charged. An I/O pin may be used to discharge the

capacitor on a periodic basis to prevent it from getting fully charged. Such a circuit would

also help in detecting failure of the flash memory and the V

DD3VFL

rail.

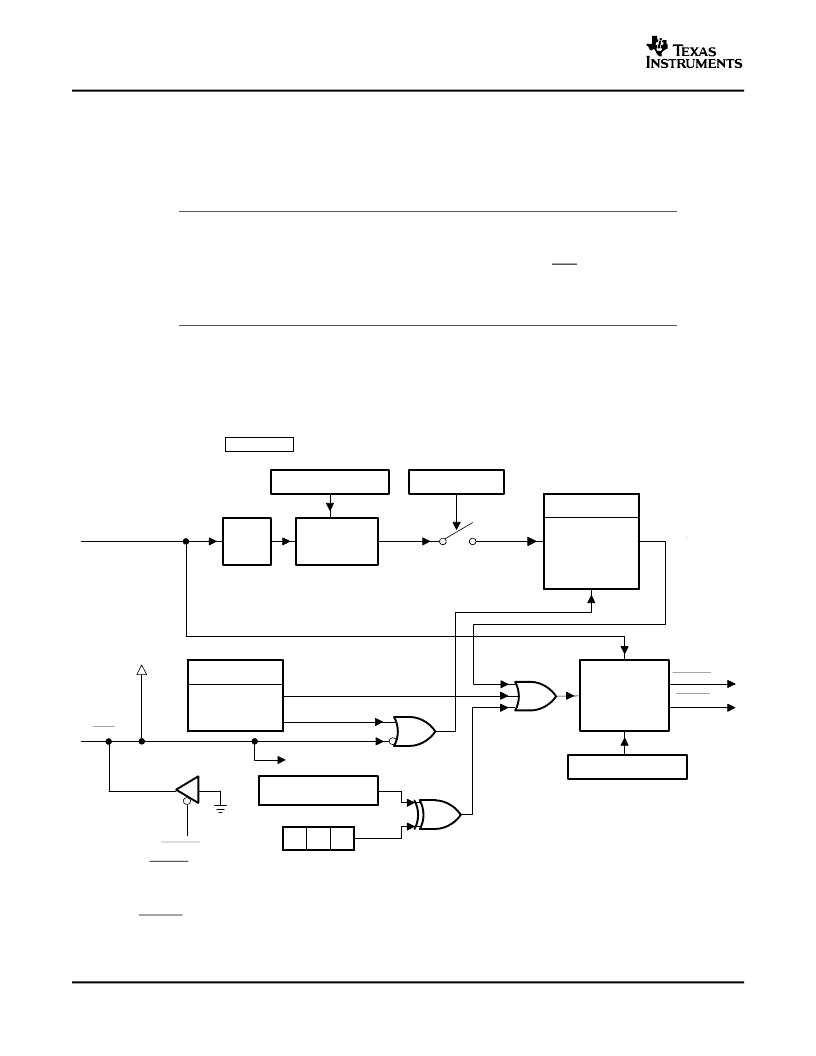

The watchdog block on the 280x is similar to the one used on the 240x and 281x devices. The watchdog

module generates an output pulse, 512 oscillator clocks wide (OSCCLK), whenever the 8-bit watchdog up

counter has reached its maximum value. To prevent this, the user disables the counter or the software

must periodically write a 0x55 + 0xAA sequence into the watchdog key register which will reset the

watchdog counter.

Figure 3-12

shows the various functional blocks within the watchdog module.

A.

The WDRST signal is driven low for 512 OSCCLK cycles.

Figure 3-12. Watchdog Module

The WDINT signal enables the watchdog to be used as a wakeup from IDLE/STANDBY mode.

44

Functional Overview

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS320F2808GGMQ | Digital Signal Processors |

| TMS320DM642GNZ720 | Video/Imaging Fixed-Point Digital Signal Processor |

| TMS320C6711GLSA167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMS320VC5402GGU | FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMS320UVC5402GGU | FIXED-POINT DIGITAL SIGNAL PROCESSOR |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMS320VC33PGE120 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320VC33PGE-120 | 制造商:Texas Instruments 功能描述:IC DSP PROCESSOR 320VC33 LQFP144 制造商:Texas Instruments 功能描述:IC, DSP PROCESSOR, 320VC33, LQFP144 |

| TMS320VC33PGE-120 | 制造商:Texas Instruments 功能描述:IC DSP PROCESSOR 320VC33 LQFP144 |

| TMS320VC33PGE120G4 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

| TMS320VC33PGE150 | 功能描述:數(shù)字信號(hào)處理器和控制器 - DSP, DSC Digital Signal Proc RoHS:否 制造商:Microchip Technology 核心:dsPIC 數(shù)據(jù)總線寬度:16 bit 程序存儲(chǔ)器大小:16 KB 數(shù)據(jù) RAM 大小:2 KB 最大時(shí)鐘頻率:40 MHz 可編程輸入/輸出端數(shù)量:35 定時(shí)器數(shù)量:3 設(shè)備每秒兆指令數(shù):50 MIPs 工作電源電壓:3.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TQFP-44 安裝風(fēng)格:SMD/SMT |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。