- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384012 > TMC22091R0C (FAIRCHILD SEMICONDUCTOR CORP) Digital Video Encoders/Layering Engine PDF資料下載

參數(shù)資料

| 型號: | TMC22091R0C |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | Digital Video Encoders/Layering Engine |

| 中文描述: | COLOR SIGNAL ENCODER, PQCC84 |

| 封裝: | PLASTIC, LCC-84 |

| 文件頁數(shù): | 37/60頁 |

| 文件大小: | 293K |

| 代理商: | TMC22091R0C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁

PRODUCT SPECIFICATION

TMC22091/TMC22191

37

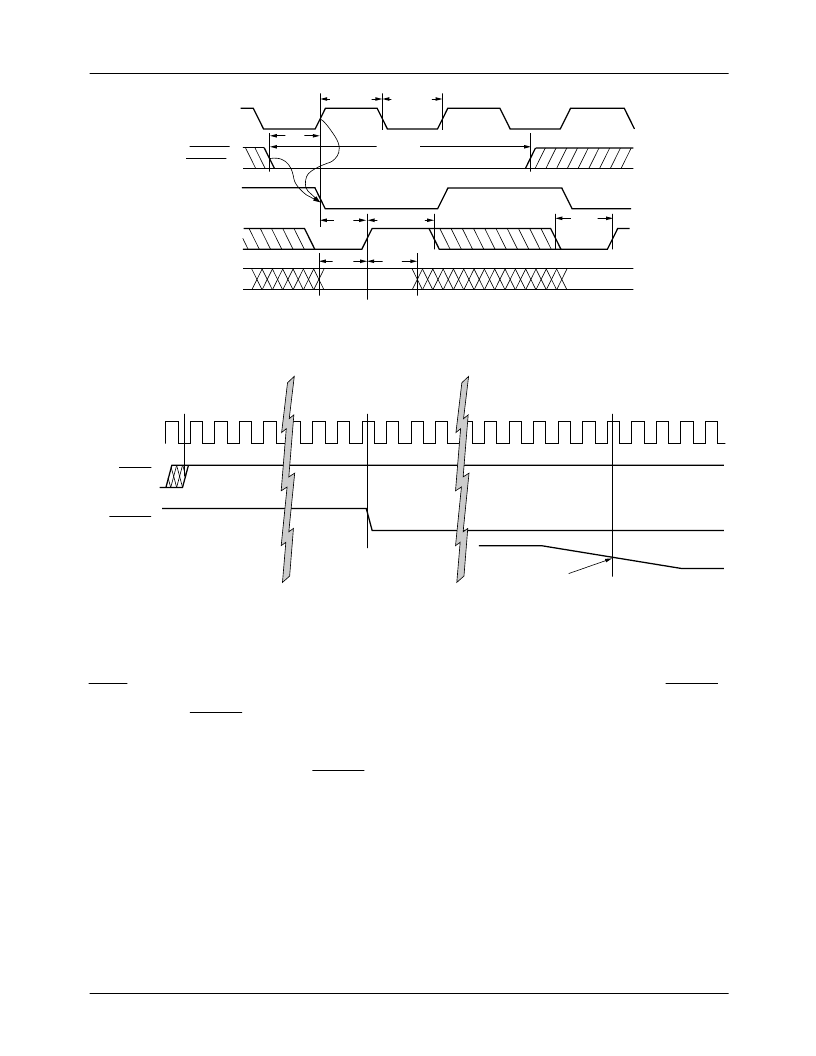

Master Mode

In Master mode, initial timing is determined from the

RESET input, and subsequent cycles result from pro-

grammed values in the Timing Control Registers. The Hori-

zontal Sync output, VHSYNC, goes LOW 18 PXCK clock

cycles after the device is reset. The 50% point of the falling

edge of sync LOW on line 4 of field 1 (NTSC) or line 1 of

field 1 (PAL) occurs at the COMPOSITE and LUMA out-

puts 56 clocks after reset, or 38 clocks after VHSYNC. See

Figure 14, Master Mode Timing.

Slave Mode

In Slave mode, the 50% point of the falling edge of sync

occurs 46 PXCK clocks after the falling edge of VHSYNC,

which is an input signal to the TMC22x91. This must be pro-

vided by the host to begin every line. If it is early, the line

will be started early, maintaining the 52 clock delay to out-

put. If it comes late, the front porch portion of the output

waveform will be extended as necessary. See Figure 15,

Slave Mode Timing.

Figure 13. Slave Mode PD Port Interface Timing (Genlock Mode)

Figure 14. Master Mode Timing

tPWHPX

tSP

PXCK

PCK

LDV

PD

KEY

VHSYNC

(GHSYNC)

tSP

tHP

tXL

24340A

tPWHLDV

tPWLLDV

2N+1

2N+2

2N+3

tPWLVH

tPWLPX

PXCK

0

50% Sync Amplitude

24353A

1

2

3

4

16

17

18

19

20

21

51

52

53

54

55

56

57

58

59

60

RESET

COMPOSITE

OUTPUT

VHSYNC

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMC22191R0C | Digital Video Encoders/Layering Engine |

| TMC22091 | Digital Video Encoders(數(shù)字視頻編碼器) |

| TMC22191 | Digital Video Encoders(數(shù)字視頻編碼器) |

| TMC2242A | Digital Half-Band Interpolating/Decimating Filter 12-bit In/16-bit Out, 60 MHz |

| TMC2242BKTC | Digital Half-Band Interpolating/Decimating Filter 12-bit In/16-bit Out, 60 MHz |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TMC22091R0CT | 功能描述:視頻 IC D/V Encoder Layering Engine RoHS:否 制造商:Fairchild Semiconductor 工作電源電壓:5 V 電源電流:80 mA 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-28 封裝:Reel |

| TMC22091ROC-T | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC22151AKHC | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

| TMC22151KHC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| TMC22152AKHC | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Multistandard Digital Video Decoder Three-Line Adaptive Comb Decoder Family, 8 & 10 bit |

發(fā)布緊急采購,3分鐘左右您將得到回復。