- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359295 > TM2SN64EPU-12A (Texas Instruments, Inc.) SYNCHRONOUS DYNAMIC RAM MODULES PDF資料下載

參數(shù)資料

| 型號(hào): | TM2SN64EPU-12A |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 存儲(chǔ)器模塊 |

| 英文描述: | SYNCHRONOUS DYNAMIC RAM MODULES |

| 中文描述: | 同步動(dòng)態(tài)RAM模塊 |

| 文件頁(yè)數(shù): | 12/16頁(yè) |

| 文件大小: | 271K |

| 代理商: | TM2SN64EPU-12A |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)當(dāng)前第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)

TM2SN64EPU 2097152 BY 64-BIT

TM4SN64EPU 4194304 BY 64-BIT

SYNCHRONOUS DYNAMIC RAMMODULES

SMMS681 – AUGUST 1997

12

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251–1443

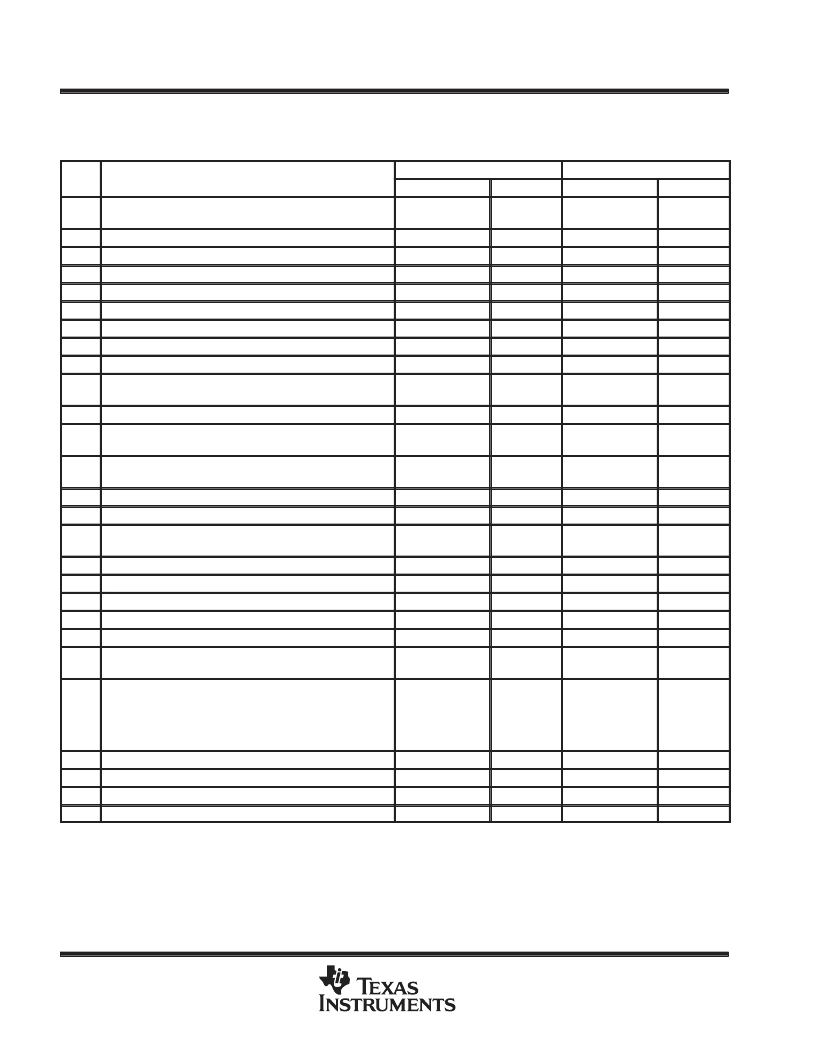

serial presence detect (continued)

Table 2. Serial Presence-Detect Data for the TM4SN64EPU

BYTE

NO.

DESCRIPTION OF FUNCTION

TM4SN64EPU-12A

TM4SN64EPU-12

ITEM

DATA

ITEM

DATA

0

Defines number of bytes written into serial memory during

module manufacturing

128 bytes

80h

128 bytes

80h

1

Total number of bytes of SPD memory device

256 bytes

08h

256 bytes

08h

2

Fundamental memory type (FPM, EDO, SDRAM, . . .)

SDRAM

04h

SDRAM

04h

3

Number of row addresses on this assembly

11

0Bh

11

0Bh

4

Number of column addresses on this assembly

9

09h

9

09h

5

Number of module banks on this assembly

2 banks

02h

2 banks

02h

6

Data width of this assembly

64 bits

40h

64 bits

40h

7

Data width continuation

00h

00h

8

Voltage interface standard of this assembly

LVTTL

01h

LVTTL

01h

9

SDRAM cycle time at maximum supported CAS latency

(CL), CL = X

tCK = 12 ns

C0h

tCK = 12 ns

C0h

10

SDRAM access from clock at CL = X

tAC = 9 ns

90h

tAC = 9 ns

90h

11

DIMM configuration type (non-parity, parity, error correcting

code [ECC])

Non-Parity

00h

Non-Parity

00h

12

Refresh rate/type

15.6

μ

s/

self-refresh

80h

15.6

μ

s/

self-refresh

80h

13

SDRAM width, primary DRAM

x8

08h

x8

08h

14

Error-checking SDRAM data width

N/A

00h

N/A

00h

15

Minimum clock delay, back-to-back random column

addresses

1 CK cycle

01h

1 CK cycle

01h

16

Burst lengths supported

1, 2, 4, 8

0Fh

1, 2, 4, 8

0Fh

17

Number of banks on each SDRAM device

2 banks

02h

2 banks

02h

18

CAS latencies supported

2, 3

06h

2, 3

06h

19

CS latency

0

01h

0

01h

20

Write latency

0

01h

0

01h

21

SDRAM module attributes

Non-buffered/

Non-registered

00h

Non-buffered/

Non-registered

00h

22

SDRAM device attributes: general

VDD tolerance =

(+10%)/(–5%).

Burst read/write,

precharge all,

auto precharge

1Eh

VDD tolerance =

(+10%),

Burst read/write,

precharge all,

auto precharge

0Eh

23

Minimum clock cycle time at CL = X – 1

tCK = 15 ns

tAC = 9 ns

N/A

F0h

tCK = 18 ns

tAC = 10 ns

N/A

30h

24

Maximum data-access time from clock at CL = X – 1

90h

A0h

25

Minimum clock cycle time at CL = X – 2

00h

00h

26

Maximum data-access time from clock at CL = X – 2

N/A

00h

N/A

00h

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TMS3121 | QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS |

| TMS3121JC | QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS |

| TMS3121NC | QUADRUPLE 80-, 64-BIT STATIC SHIFT REGISTERS |

| TMS3123 | HEX 32-BIT STATIC SHIFT REGISTERS |

| TMS3123NC | HEX 32-BIT STATIC SHIFT REGISTERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TM2SR72EPH | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SYNCHRONOUS DYNAMIC RAM MODULES |

| TM2SR72EPN | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SYNCHRONOUS DYNAMIC RAM MODULES |

| TM2SR72EPU | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SYNCHRONOUS DYNAMIC RAM MODULES |

| TM2TR64EPH | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SYNCHRONOUS DYNAMIC RAM MODULES |

| TM2USBABDEV1 | 制造商:Schneider Electric 功能描述:M238 SoMachine Program Loading Device |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。