- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98263 > TLV987CPFB (TEXAS INSTRUMENTS INC) SPECIALTY ANALOG CIRCUIT, PQFP48 PDF資料下載

參數(shù)資料

| 型號: | TLV987CPFB |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 模擬信號調(diào)理 |

| 英文描述: | SPECIALTY ANALOG CIRCUIT, PQFP48 |

| 封裝: | PLASTIC, TQFP-48 |

| 文件頁數(shù): | 15/21頁 |

| 文件大?。?/td> | 285K |

| 代理商: | TLV987CPFB |

TLV987

3-V 10-BIT 27 MSPS AREA CCD SENSOR

SIGNAL PROCESSOR

SLAS211A – MARCH 1999 – REVISED SEPTEMBER 1999

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

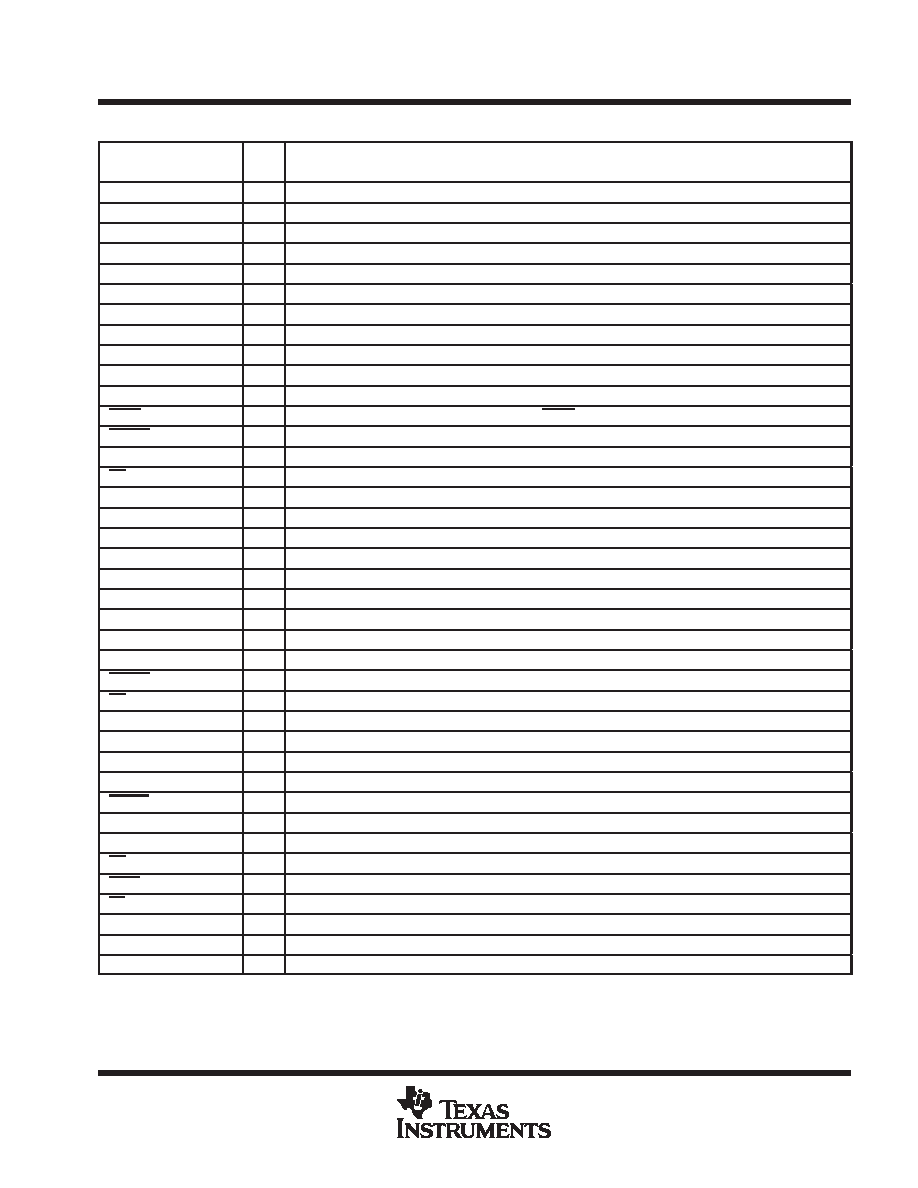

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

ADCCLK

25

I

ADC clock input.

AGND1

44

Analog ground for internal CDS circuits

AGND2

4

Analog ground for internal PGA circuits

AGND3

20

Analog ground for internal DAC circuits

AGND4

32

Analog ground for internal ADC circuits

AGND5

37

Analog ground for internal REF circuits

AVDD1

43

Analog supply voltage for internal CDS circuits, 3 V

AVDD2

3

Analog supply voltage for internal PGA circuits, 3 V

AVDD3

19

Analog supply voltage for internal DAC circuits, 3 V

AVDD4

33

Analog supply voltage for internal ADC circuits, 3 V

AVDD5

41

Analog supply voltage for internal ADC circuits, 3 V

BLKG

36

I

Control input. CDS operation is disabled when BLKG is pulled low.

CLAMP

47

I

CCD signal clamp control input

CLREF

48

O

Clamp reference voltage output.

CS

28

I

Chip select. A logic low on this input enables the TLV987.

DACO1

21

O

Digital-to-analog converter output1

DACO2

22

O

Digital-to-analog converter output2

DACT

23

O

MUXed test output for internal offset DACs

DGND

5

Digital ground

DIGND

18

Digital interface circuit ground

DIN

1

I

Input signal from CCD

DIVDD

17

Digital interface circuit supply voltage, 1.8 V to 4.4 V

DVDD

6

Digital supply voltage, 3 V

D0 – D9

7 – 16

O

10-bit three-state ADC output data or offset DACs test data

OBCLP

31

I

Optical black level and offset calibration control input. Active low.

OE

24

I

Output data enable. Active low.

PIN

2

I

Input signal from CCD

RBD

38

O

Internal bandgap reference for external decoupling

RMD

39

O

Ref– output for external decoupling

RPD

40

O

Ref+ output for external decoupling

RESET

29

I

Hardware reset input, active low. This signal forces a reset of all internal registers.

SCLK

26

I

Serial clock input. This clock synchronizes the serial data transfer.

SDIN

27

I

Serial data input to configure the internal registers.

SR

45

I

CCD reference level sample clock input

STBY

30

I

Hardware power-down control input, active low

SV

46

I

CCD signal level sample clock input

TPM

34

O

MUXed test output: PGA noninverting output or inverted PGA clock

TPP

35

O

MUXed test output: PGA inverting output or inverted CDS clock

VSS

42

Silicon substrate, normally connected to analog ground

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV990-13PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV990-13PFBG4 | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV990-21PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV990-21PFBG4 | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

| TLV990-28PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV987PFB | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V 10-BIT 27 MSPS AREA CCD SENSOR SIGNAL PROCESSOR |

| TLV990 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V, 10-BIT, 28-MSPS AREA CCD AND VIDEO SIGNAL PROCESSOR |

| TLV990-13 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V, 10-BIT, 13-MSPS AREA CCD ANALOG FRONT END |

| TLV990-13PFB | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 CCD Sig Processor/ Digitizer Designed RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

| TLV990-13PFBG4 | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 CCD Sig Processor/ Digitizer Designed RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。