- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371186 > TLV320AC56PT (Texas Instruments, Inc.) 3-V VOICE-BAND AUDIO PROCESSORS VBAPE PDF資料下載

參數(shù)資料

| 型號: | TLV320AC56PT |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | 3-V VOICE-BAND AUDIO PROCESSORS VBAPE |

| 中文描述: | 3伏的語音頻帶音頻處理器VBAPE |

| 文件頁數(shù): | 25/46頁 |

| 文件大小: | 452K |

| 代理商: | TLV320AC56PT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁當(dāng)前第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

SLAS428 AUGUST 2004

www.ti.com

25

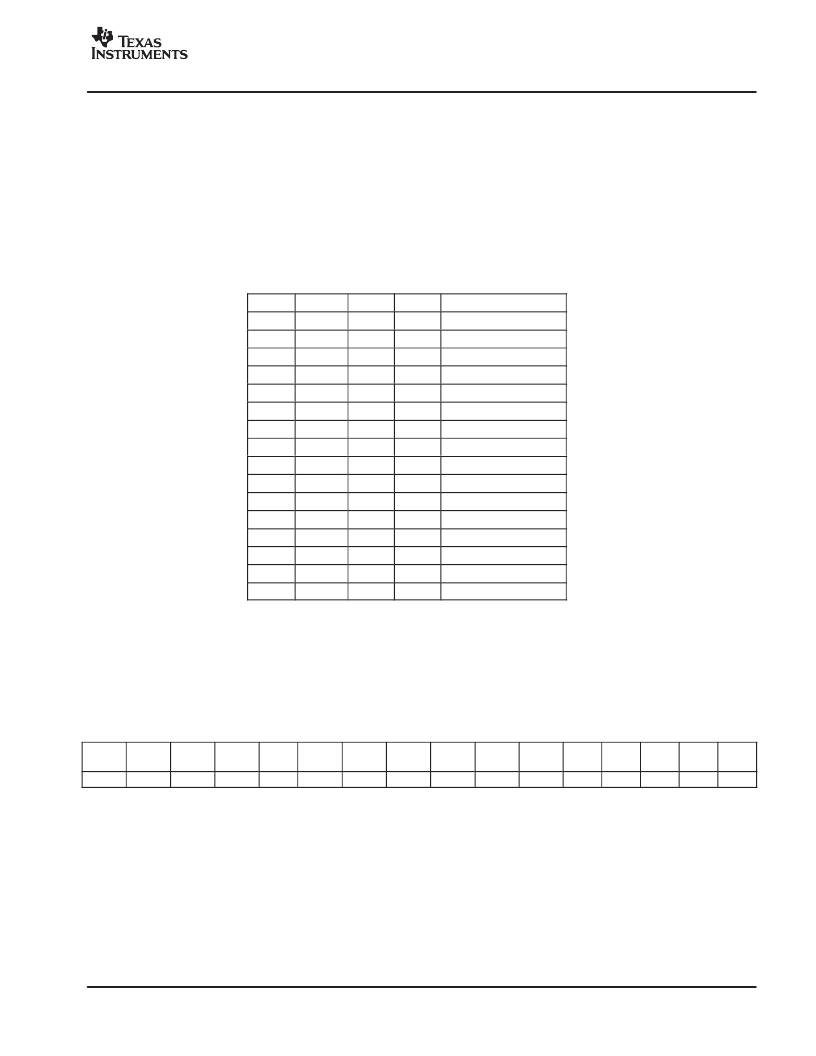

’DAC26 COMMUNICATION PROTOCOL

Register Programming

The ’DAC26 is entirely controlled by registers. An SPI master controlls the reading and writing of these registers by the

use of a 16-bit command, which is sent prior to the data for that register. The command is constructed as shown in Figure 19.

The command word begins with a R/W bit, which specifies the direction of data flow on the SPI serial bus. The following

four bits specify the page of memory this command is directed to, as shown in Table 2. The next six bits specify the register

address on that page of memory to which the data is directed. The last five bits are reserved for future use and should be

written only with zeros.

Table 2. Page Addressing

PG3

0

PG2

0

PG1

0

PG0

0

PAGE ADDRESSED

0

0

0

0

1

1

0

0

1

0

2

0

0

1

1

Reserved

0

1

0

0

Reserved

0

1

0

1

Reserved

0

1

1

0

Reserved

0

1

1

1

Reserved

1

0

0

0

Reserved

1

0

0

1

Reserved

1

0

1

0

Reserved

1

0

1

1

Reserved

1

1

0

0

Reserved

1

1

0

1

Reserved

1

1

1

0

Reserved

1

1

1

1

Reserved

To read all the first page of memory, for example, the host processor must send the command 0x8000 to the ’DAC26 – this

specifies a read operation beginning at page 0, address 0. The processor can then start clocking data out of the ’DAC26.

The ’DAC26 automatically increments its address pointer to the end of the page; if the host processor continues clocking

data out past the end of a page, the ’DAC26 sends back the value 0xFFFF.

Likewise, writing to page 1 of memory consists of the processor writing the command 0x0800, which specifies a write

operation, with PG0 set to 1, and all the ADDR bits set to 0. This results in the address pointer pointing at the first location

in memory on Page 1. See the section on the ’DAC26 memory map for details of register locations

BIT 15

MSB

BIT 14

BIT 13

BIT 12

BIT 11

BIT 10

BIT 9

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

BIT 1

BIT 0

LSB

R/W*

PG3

PG2

PG1

PG0

ADDR5

ADDR4

ADDR3

ADDR2

ADDR1

ADDR0

0

0

0

0

0

Figure 19. ’DAC26 Command Word

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC20I | Layout and Grounding Guidelines for TLV320AIC2x |

| TLV320AIC10PFB | ECONOLINE: RSS & RSD - 1kVDC and 3KVDC Isolation- Internal SMD Construction- UL94V-0 Package Material- Toroidal Magnetics- Efficiency to 85%- SMD5, SMD8, SMD10 and SMD12 case styles |

| TLV320AC57DW | 3-V VOICE-BAND AUDIO PROCESSORS VBAPE |

| TLV320AIC24C | Layout and Grounding Guidelines for TLV320AIC2x |

| TLV320AIC24I | Layout and Grounding Guidelines for TLV320AIC2x |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV320AC57 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V VOICE-BAND AUDIO PROCESSORS VBAPE |

| TLV320AC57DW | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V VOICE-BAND AUDIO PROCESSORS VBAPE |

| TLV320AC57N | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V VOICE-BAND AUDIO PROCESSORS VBAPE |

| TLV320AC57PT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3-V VOICE-BAND AUDIO PROCESSORS VBAPE |

| TLV320AD11A | 制造商:TI 制造商全稱:Texas Instruments 功能描述:3.3 V INTEGRATED ADSL OVER POTS CODEC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。