- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373626 > TDA9115 (意法半導(dǎo)體) LOW-COST I2C CONTROLLED DEFLECTION PROCESSOR FOR MULTISYNC MONITOR PDF資料下載

參數(shù)資料

| 型號: | TDA9115 |

| 廠商: | 意法半導(dǎo)體 |

| 英文描述: | LOW-COST I2C CONTROLLED DEFLECTION PROCESSOR FOR MULTISYNC MONITOR |

| 中文描述: | 低費用的I2C可控?fù)隙榷嗤斤@示器處理器 |

| 文件頁數(shù): | 24/45頁 |

| 文件大?。?/td> | 579K |

| 代理商: | TDA9115 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當(dāng)前第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

TDA9115

24/45

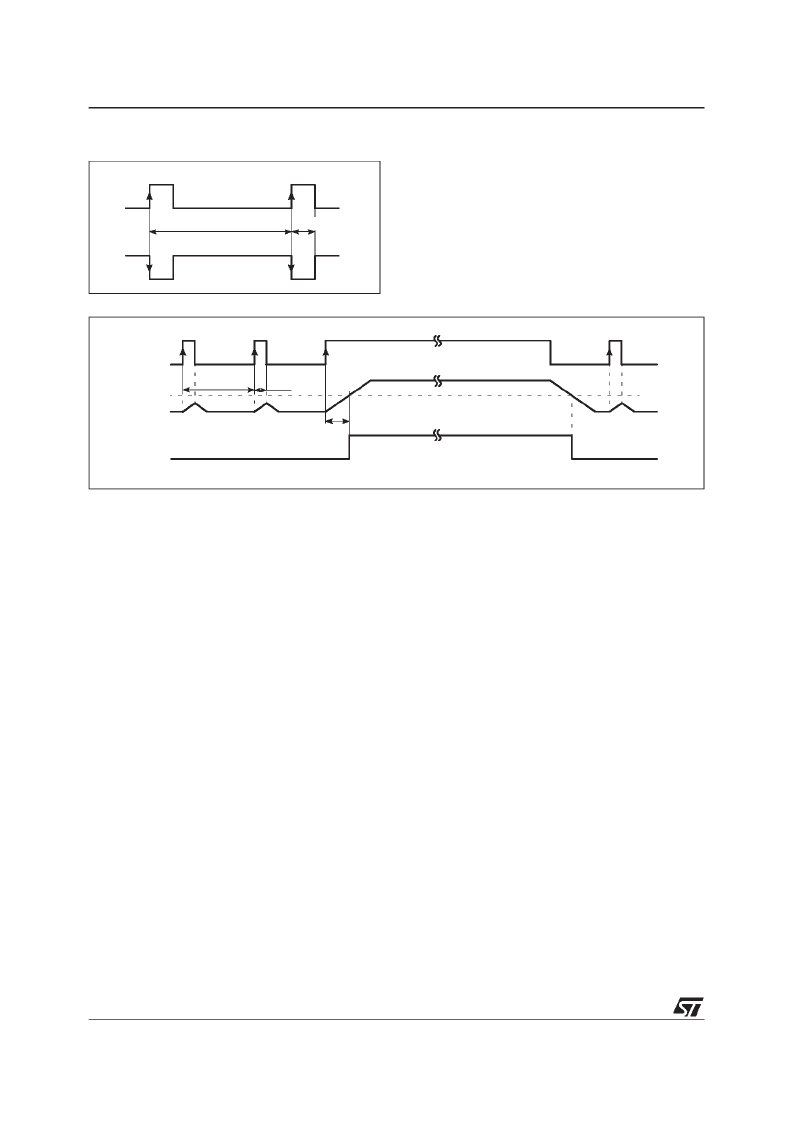

Figure 2. Horizontal sync signal

Figure 3. Extraction of V-sync signal from H/V-sync signal

9.2.2 Automatic sync. selection mode

I

2

C busbit VSyncAuto is set to 1. In this mode, the

device itself controls the I

2

C bus bits switching the

polarity inverters and the vertical sync. signal se-

lector (VSyncSel), using the information provided

by detection circuitry. If both extracted and pure

vertical sync. signals are present, the one already

selected is maintained. No intervention of the

MCU is necessary.

9.3 HORIZONTAL SECTION

9.3.1 General

The horizontal section consists of two PLLs with

various adjustments and corrections, working on

horizontal deflection frequency, then phase shift-

ing and output driving circuitry providing H-drive

signal on HOut pin. Input signal to the horizontal

section is output of the polarity inverter on H/

HVSyn input. The device ensures automatically

that this polarity be always positive.

9.3.2 PLL1

The PLL1 block diagram is in Figure 5. It consists

of a voltage controlled oscillator (VCO), a shaper

with adjustablethreshold, a charge pumpwith inhi-

bition circuit, a frequency and phase comparator

and timing circuitry. The goal of the PLL1 is to

make theVCO ramp signal match in frequency the

sync. signal and to lock this ramp in phase to the

sync. signal, with a possibility to adjust a perma-

nent phase offset. On the screen, this offset re-

sults inthe change ofhorizontal position of thepic-

ture. The loop, by tuning the VCO accordingly,

gets and maintains in coincidence the rising edge

of input sync. signal with signal REF1, which is de-

rived from the VCO ramp by a comparator with

threshold adjustable through HPOS I

2

C bus con-

trol. The coincidence is identified and flagged by

lock detection circuit on pin HLckVBk .

The charge pump provides positive and negative

currents charging the external loop filter on HPosF

pin. The loop is independent of the trailing edge of

sync. signal and only locks to its leading edge. By

design, the PLL1 does not suffer from any dead

band even while locked. The speed of the PLL1

depends on the current value provided by the

charge pump. While not locked, the current is very

low, to slow down the changes of VCO frequency

and thus protect the external power components

at sync. signal change. In locked state, the cur-

rents are much higher, two different values being

selectable via PLL1Pump I

2

C bus bit to provide a

mean to control the PLL1 speed by S/W. Lower

values make the PLL1 slower, but more stable.

Higher values make it faster and less stable. In

general, the PLL1 speed should be higher for high

deflection frequencies. The response speed and

stability (jitter level) depends on the choice of ex-

ternal components making up the loop filter. A

“CRC” filter is generally used (see Figure 4 on

page 25).

Positive

Negative

T

H

t

PulseHSyn

H/V-sync

Integration

Extracted

V-sync

t

extrV

T

H

t

PulseHsyn

Internal

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TDA9116 | LOW-COST I2C CONTROLLED DEFLECTION PROCESSOR FOR MULTISYNC MONITOR |

| TDA9201 | WIDE BAND VIDEO PREAMPLIFIER |

| TDA9203 | I2C BUS CONTROLLED 70MHz RGB PREAMPLIFIER |

| TDA9203A | I2C BUS CONTROLLED 70MHz RGB PREAMPLIFIER |

| TDA9206 | I2C BUS CONTROLLED 130MHz RGB PREAMPLIFIER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDA9116 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:LOW-COST I2C CONTROLLED DEFLECTION PROCESSOR FOR MULTISYNC MONITOR |

| TDA9118 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:行/場掃描處理電路 |

| TDA9141 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:PAL/NTSC/SECAM decoder/sync processor |

| TDA9143 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:I2C-bus controlled, alignment-free PAL/NTSC/SECAM decoder/sync processor |

| TDA9144 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:I2C-bus controlled, alignment-free PAL/NTSC/SECAM decoder/sync processor with PALplus helper demodulator |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。