- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄371182 > TDA6509TT (NXP SEMICONDUCTORS) 3-band mixer/oscillator and PLL for terrestrial tuners PDF資料下載

參數(shù)資料

| 型號: | TDA6509TT |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 調(diào)諧器 |

| 英文描述: | 3-band mixer/oscillator and PLL for terrestrial tuners |

| 中文描述: | 3-BAND, VIDEO TUNER, PDSO32 |

| 封裝: | 6.10 MM, 0.65 MM PITCH, PLASTIC, MO-153, SOT487-1, TSSOP-32 |

| 文件頁數(shù): | 10/42頁 |

| 文件大?。?/td> | 274K |

| 代理商: | TDA6509TT |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

2005 Mar 25

10

Philips Semiconductors

Product specification

3-band mixer/oscillator and PLL for

terrestrial tuners

TDA6508; TDA6508A;

TDA6509; TDA6509A

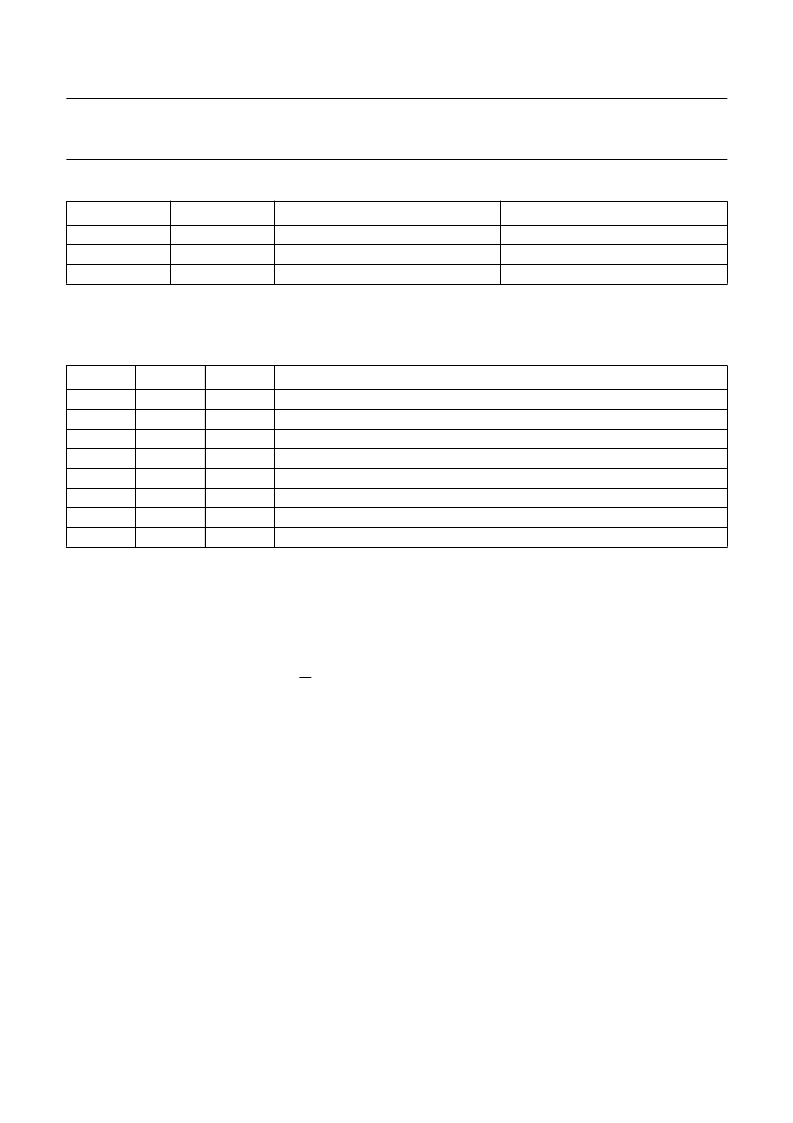

Table 4

Reference divider ratio selection bits

Note

1.

Crystal oscillator frequency or externally sourced reference frequency of 4 MHz at pin XTAL_REF.

Table 5

Test mode selection bits

Notes

1.

2.

3.

This is the default mode at power-on reset.

1

2

f

div

is output from port P3 when the charge-pump is off.

Port P3 cannot be used when these test modes are active.

RSA

RSB

REFERENCE DIVIDER RATIO

FREQUENCY STEP (kHz)

(1)

X

0

1

0

1

1

80

128

64

50

31.25

62.5

T2

T1

T0

TEST MODE

0

0

0

0

1

1

1

1

0

0

1

1

1

1

0

0

0

1

0

1

0

1

0

1

normal mode (read and write mode bytes allowed)

normal mode (read and write mode bytes allowed)

(1)

charge-pump is off

(2)

byte BB ignored

charge-pump sinks current

charge-pump sources current

1

2

f

ref

is output from port P3

(3)

1

2

f

div

is output from port P3

(3)

8.3

Read mode

The read mode is defined by setting bit R/W to logic 1 in

address byte ADB; see Table 6.

After the slave address has been recognized, the device

generates an acknowledge pulse, and status byte SB is

transferredontheSDA line(MSB first).Dataisvalidonthe

SDA line when pin SCL is HIGH. A second data byte can

be read from the device if the microcontroller generates an

acknowledge on the SDA line (master acknowledge).

End of transmission will occur if no master acknowledge is

asserted.Thedevicewillthenreleasethedatalinetoallow

the microcontroller to generate a STOP condition.

Bit POR is set to logic 1 at power-on. This bit is reset when

an end-of-data is detected by the device at the end of a

read sequence. Bit FL controls the PLL by indicating when

the loop is locked (bit FL = 1).

The internal ADC can be used to apply AFC information to

a microcontroller in the IF section of the television via

status byte bits A0, A1 and A2. Up to five voltage levels

can be applied to the ADC input pin ADC; the resultant

values of bits A2, A1 and A0 are shown in Table 8.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TDA8007B | IC LOGIC 1G02 SINGLE 2-INPUT POSITIVE-NOR GATE -40+85C SOT-23-5 3000/REEL |

| TDA8012A | Low power PLL FM demodulator for satellite TV receivers |

| TDA8012AM | Low power PLL FM demodulator for satellite TV receivers |

| TDA8020 | Dual smart card interface |

| TDA8260 | Satellite Zero-IF QPSK/8PSK downconverter with PLL synthesizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TDA6600-2 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:TV Stereo Decoder with Matrix Preliminary Data |

| TDA6610-2 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:TV-STEREO PROCESSOR |

| TDA6610-5 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:TV STEREO PROCESSOR |

| TDA6611 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:TV STEREO PROCESSOR |

| TDA6612 | 制造商:INFINEON 制造商全稱:Infineon Technologies AG 功能描述:TV-STEREO-SOUND |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。