- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373563 > TC3011 (Electronic Theatre Controls, Inc.) Turbo Product Code decoders PDF資料下載

參數(shù)資料

| 型號(hào): | TC3011 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | Turbo Product Code decoders |

| 中文描述: | Turbo乘積碼解碼器 |

| 文件頁數(shù): | 2/2頁 |

| 文件大?。?/td> | 42K |

| 代理商: | TC3011 |

This document contains preliminary information. Information is subject to change without notice.

TC3000 is covered by several patents.

Flexibility

TC3000 family offers 3 levels of flexibility :

TC3000 family member

VHDL generic parameters

before synthesis

On-the fly parameters

from block to block

9

BCH t=2 code support (YES/NO)

9

Choice on bitrate

9

Maximum row code length

9

Maximum column code length

9

Input Quantization width

9

1 or 2 input buffers

9

Row code

9

Column code

9

Shortening values

9

Max. number of iterations

9

Stopping feature enabled

FEC performance

Very high FEC performance are obtained for various block sizes and coding rates. The FEC behaviour

of the

“

BCH t=2

”

codes makes them particularly attractive for quasi-error free applications.

Gaussian channel and QPSK modulation. Results given with 5 iterations.

Product Code

Rate Eb/N0 @BER=10

-5

Eb/N0 @BER=10

-8

(32,26) x (32,26)

0.660

(32,21) x (32,21)

0.431

(64,57) x (64,57)

0.793

(64,51) x (64,51)

0.635

(128,120) x (128,120) 0.879

(128,113) x (128,113) 0.779

(256,247) x (256,247) 0.931

(256,239) x (256,239) 0.872

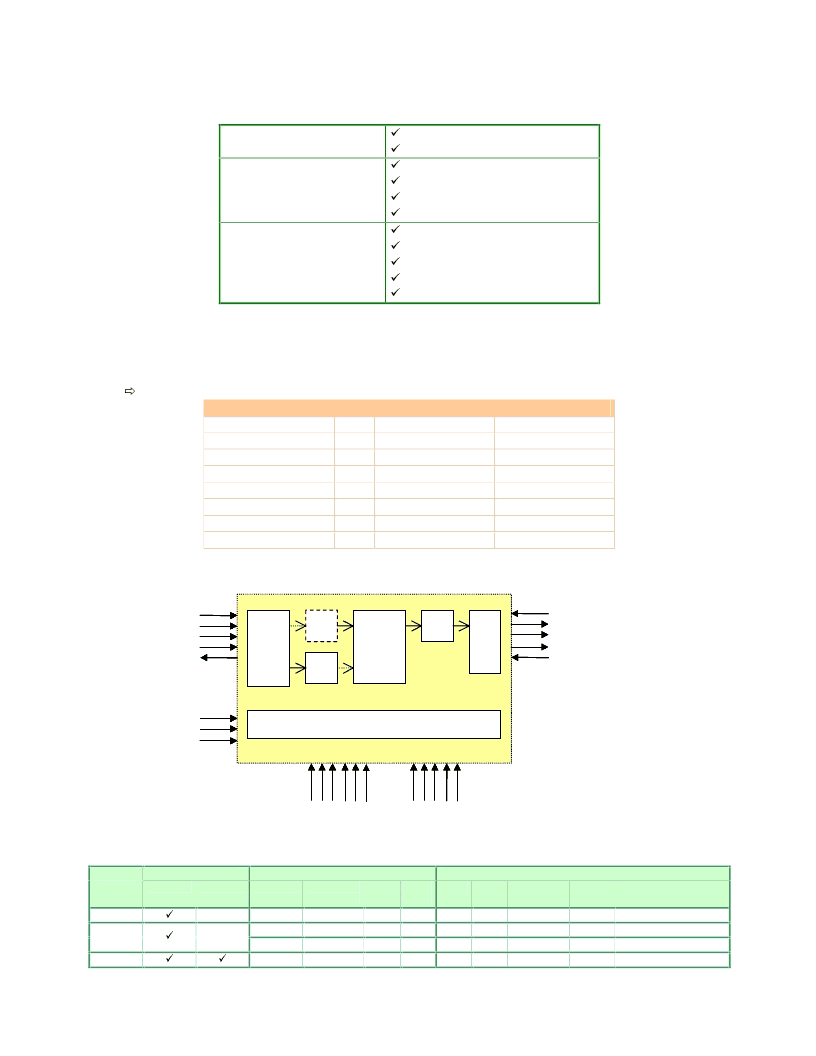

Block Diagram

2.9 dB

2.4 dB

3.2 dB

2.6 dB

3.8 dB

3.3 dB

4.5 dB

4.0 dB

3.6 dB

N.A.

3.6 dB

2.9 dB

4.2 dB

3.4 dB

4.8 dB

N.A.

Implementation results

Codes supported

Product

Hamming

Generic parameter setting

Row max.

length

max. length

64

64

64

64

128

128

64

64

Implementation results

APEX20K

device

MHz

200 C7

82

200 C7

72

400 C7

67

400 C7

79

BCH t=2

Column

Data

width

4

4

4

4

bank

swap

NO

NO

NO

NO

LE

ESB

Fmax

Typical Bitrate

@(64,57)

2

, 5 iterations

8 Mbits/s

25 Mbits/s

23.5 Mbits/s

14 Mbits/s

TC3011

TC3014

9

2025

6926

8115

8932

22

36

88

24

9

TC3022

9

9

module

Configuration module

DRDY

D[D_WIDTH-1:0]

DEN

TC3000

DBLK

Interface

MSELECT

QRDY

Q

QEN

QBLK

Signals

Buffer #1

Buffer #0

Interface

I/Os

Interface

module

Buffer

module

Decoder

DCK

M

M

M

M

M

Input

RSTB

CK

QCK

M

T

M

T

I

Global

Input

Input

I

Output

Dedicated

Configuration

Microcontroller

Output

Output

Input

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TC3014 | Turbo Product Code decoders |

| TC3022 | Turbo Product Code decoders |

| TC3339 | CONNECTOR ACCESSORY |

| TC35083F | 10-BIT A-D CONVERTER |

| TC35083P | 10-BIT A-D CONVERTER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TC30-11EWA | 制造商:Kingbright Corporation 功能描述: |

| TC30130-001 | 制造商:Molex 功能描述:QC 3P TEE W/3P MC DROP #14 SK |

| TC30130-200 | 制造商:Molex 功能描述:QC 3P TEE W/3P MC DROP #14 SK |

| TC3014 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Turbo Product Code decoders |

| TC-3014002 | 制造商:PREMO 制造商全稱:PREMO CORPORATION S.L 功能描述:50/60 Hz industrial Current Transformer up to 600A |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。