- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98158 > TAS3204PAG (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PQFP64 PDF資料下載

參數(shù)資料

| 型號: | TAS3204PAG |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | GREEN, PLASTIC, TQFP-64 |

| 文件頁數(shù): | 2/76頁 |

| 文件大小: | 1224K |

| 代理商: | TAS3204PAG |

第1頁當(dāng)前第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁

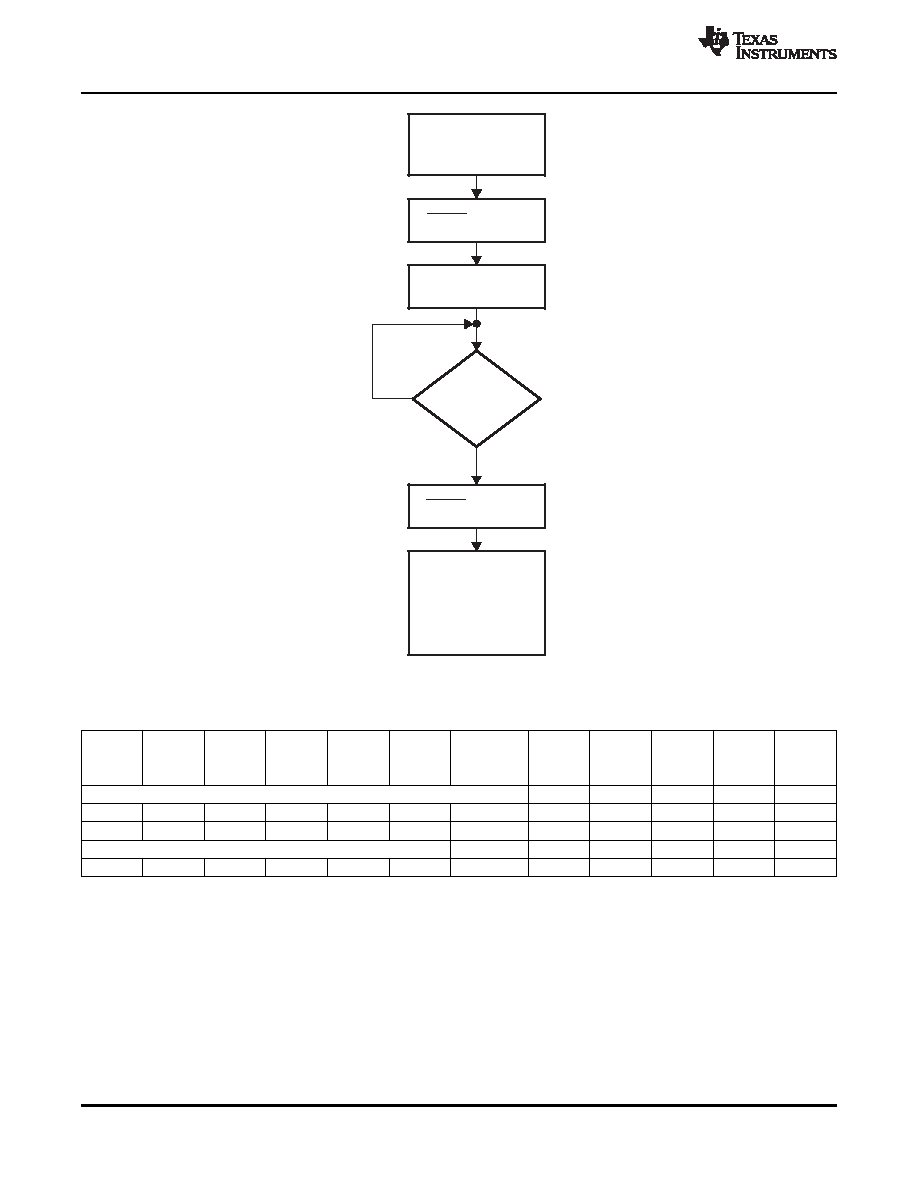

Are

Clocks

Stable?

No

Yes

RESET Pin = Low

Enable Mute and

Wait for Completion

Change fMCLK

RESET Pin = High

After

TAS3204

Initializes,

Re-initialize

I C Registers

2

SLES197C – APRIL 2007 – REVISED MARCH 2011

www.ti.com

Figure 3-2. Master Clock Frequency (fMCLK) Change Procedure

Table 3-1. TAS3204 MCLK and LRCLK Common Values (MCLK = 24.576 MHz or MCLK = 22.579 MHz)

MCLK/

MCLK

SCLKIN

SCLK_IN

SCLK_OUT

FS Sample

Ch Per

LRCLK

Ch Per

LRCLK

PLL

FDSPCLK

Freq

Rate

Freq

Rate

fDSPCLK/fS

Rate (kHz)

SDIN

Ratio

SDOUT

(FS)

Multiplier

(MHz)

(× fS)

(MHz)

(× fS)

Slave Mode, 2 Channels In, 2 Channels Out

44.1

2

512

22.579

64

2.822

64

2

64

5.5

124.2

2816

48

2

256

24.576

64

3.072

64

2

64

5.5

135.2

2816

Master Mode, 2 Channels In, 2 Channels Out

48

2

256

24.576

N/A

64

2

64

5.5

135.2

2816

10

TAS3204 Clocking System

Copyright 2007–2011, Texas Instruments Incorporated

Product Folder Link(s): TAS3204

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TAS3218IPZPR | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218IPZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218PZPR | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS3218PZP | SPECIALTY CONSUMER CIRCUIT, PQFP100 |

| TAS5000PFB | SPECIALTY CONSUMER CIRCUIT, PQFP48 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TAS3204PAGR | 功能描述:音頻 DSP Hi Perf Dual Core DSP/MCU Aud Proc RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

| TAS3208 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DIGITAL AUDIO PROCESSOR WITH ANALOG INTERFACE |

| TAS3208EVM | 功能描述:音頻 IC 開發(fā)工具 TAS3208EVM Eval Mod RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| TAS3208EVM-LC | 功能描述:音頻 IC 開發(fā)工具 TAS3208 Low Cost EVM RoHS:否 制造商:Texas Instruments 產(chǎn)品:Evaluation Kits 類型:Audio Amplifiers 工具用于評估:TAS5614L 工作電源電壓:12 V to 38 V |

| TAS3208IPZP | 功能描述:音頻 DSP Dual Core Dig Aud Proc RoHS:否 制造商:Texas Instruments 工作電源電壓: 電源電流: 工作溫度范圍: 安裝風(fēng)格: 封裝 / 箱體: 封裝:Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。