- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373531 > T7906EDDMQ (ATMEL CORP) Single Point to Point IEEE 1355 High Speed Controller PDF資料下載

參數(shù)資料

| 型號: | T7906EDDMQ |

| 廠商: | ATMEL CORP |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | Single Point to Point IEEE 1355 High Speed Controller |

| 中文描述: | 3 CHANNEL(S), 200M bps, SERIAL COMM CONTROLLER, UUC |

| 封裝: | DIE |

| 文件頁數(shù): | 7/42頁 |

| 文件大小: | 339K |

| 代理商: | T7906EDDMQ |

第1頁第2頁第3頁第4頁第5頁第6頁當(dāng)前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁

7

T7906E

Rev. A

–

27-Aug.-01

Programming the T7906E

Programming the T7906E internal registers is done via a simple protocol over the IEEE-

1355 link or directly via the host interface. The link protocol consists of a command byte

and, if necessary, one or more data bytes.

All internal registers are 8-bit wide addressable. Two commands (read and write) suffice

to access all registers of the T7906E.

The T7906E provides

registers

and

ports

; a register contains exactly one byte (read /

write), whereas a port (e.g. a FIFO interface) behaves like a FIFO, meaning that multiple

data bytes can be read or written from/to the port.

The ports of the T7906E such as the FIFO, UART, ADC and RAM interface are

accessed by a read/write command to the corresponding port address. In the case of

FIFO, Host, UART and memory interface, a packet oriented access is also possible

(meaning transferring multiple data bytes with a single command).

The read/write selection of a command is done by setting bit7 (msb) of the first byte to

one (read) or zero (write).

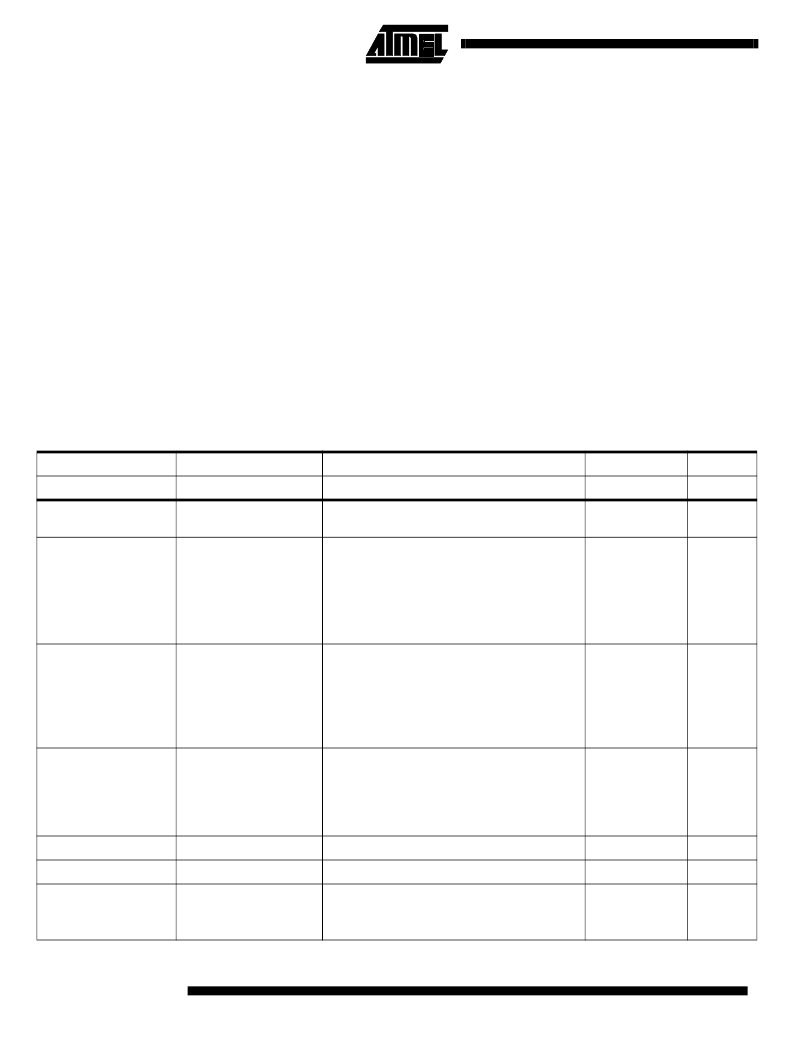

Signal Description

This section describes the signals of the T7906E. Groups of signals represent busses

where the highest number is the MSB.

Signal

Direction

Description

max. output load

Signal

[mA]

[pF]

HSEL*

I

when low, the external host selects the T7906E host

interface

HWRnRD

I

host interface write/read signal

if HWRnRD is high during HSEL* low, the host writes

data to the address register or to the T7906E

registers.

if HWRnRD is low during HSEL* low, the host reads

data from the address register or the T7906E

registers.

HDATnADR

I

host interface data/address signal

if HDATnADR is high during read, the host

reads/writes data from/to the internal T7906E

(data) registers.

if HDATnADR is low during read, the host

reads/writes address from/to the address register.

HDATA(7:0)

I/O

T7906E data bus.

This data lines will be used to access

the T7906E registers.

HDATA(7:0) can also be used as GPIO(2), if

Host interface is disabled.

3

50

HINTR*

O

host interrupt request line

3

50

TMR1_CLK

I

timer1 clock (max. 12.5 MHz)

TMR1_EXP

O

timer1 expired. Asserted for one cycle

if the value of counter1 is equal to the

content of register TPERIOD1(3:0).

3

50

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| T7906EDDSV | Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKT | Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKT-E | Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKTMQ | Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKTSV | Single Point to Point IEEE 1355 High Speed Controller |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| T7906EDDSV | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKST/883 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKT | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKT/883 | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Single Point to Point IEEE 1355 High Speed Controller |

| T7906EKT/SB | 制造商:ATMEL 制造商全稱:ATMEL Corporation 功能描述:Single Point to Point IEEE 1355 High Speed Controller |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。