- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98145 > ST72F321J7T1 (STMICROELECTRONICS) 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | ST72F321J7T1 |

| 廠商: | STMICROELECTRONICS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| 封裝: | 10 X 10 MM, PLASTIC, TQFP-44 |

| 文件頁數(shù): | 164/176頁 |

| 文件大小: | 1112K |

| 代理商: | ST72F321J7T1 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁第151頁第152頁第153頁第154頁第155頁第156頁第157頁第158頁第159頁第160頁第161頁第162頁第163頁當(dāng)前第164頁第165頁第166頁第167頁第168頁第169頁第170頁第171頁第172頁第173頁第174頁第175頁第176頁

ST72321J

88/176

SERIAL PERIPHERAL INTERFACE (Cont’d)

10.5.4.4 Data Transfer Format

During an SPI transfer, data is simultaneously

transmitted (shifted out serially) and received

(shifted in serially). The serial clock is used to syn-

chronize the data transfer during a sequence of

eight clock pulses.

The SS pin allows individual selection of a slave

device; the other slave devices that are not select-

ed do not interfere with the SPI transfer.

Clock Phase and Clock Polarity

Four possible timing relationships may be chosen

by software, using the CPOL and CPHA bits.

The CPOL (clock polarity) bit controls the steady

state value of the clock when no data is being

transferred. This bit affects both master and slave

modes.

The combination between the CPOL and CPHA

(clock phase) bits selects the data capture clock

edge.

Caution: In all cases, the idle state of the SCK pin

must correspond to the selected polarity. The SCK

pin must be pulled up if CPOL=1, or pulled down if

CPOL=0.

Figure 55, shows an SPI transfer with the four

combinations of the CPHA and CPOL bits. The di-

agram may be interpreted as a master or slave

timing diagram where the SCK pin, the MISO pin,

the MOSI pin are directly connected between the

master and the slave device.

The SS pin is the slave device select input and can

be driven by the master device.

The master device applies data to its MOSI pin-

clock edge before the capture clock edge.

CPHA bit is set

The second edge on the SCK pin (falling edge if

the CPOL bit is reset, rising edge if the CPOL bit is

set) is the MSBit capture strobe. Data is latched on

the occurrence of the first clock transition.

No write collision should occur even if the SS pin

stays low during a transfer of several bytes (see

Figure 54).

CPHA bit is reset

The first edge on the SCK pin (falling edge if CPOL

bit is set, rising edge if CPOL bit is reset) is the

MSBit capture strobe. Data is latched on the oc-

currence of the second clock transition.

This pin must be toggled high and low between

each byte transmitted (see Figure 54).

To protect the transmission from a write collision a

low value on the SS pin of a slave device freezes

the data in its SPIDR register and does not allow it

to be altered. Therefore the SS pin must be high to

write a new data byte in the SPIDR without pro-

ducing a write collision.

Note: The SPI must be disabled by resetting the

SPE bit if the CPOL bit is changed at the commu-

nication byte boundaries.

10.5.4.5 Output Disable

In order to free the I/O pin so it can be used for oth-

er purposes, it is possible to disable the SPI output

function by setting the SOD bit in the SPICSR reg-

ister.

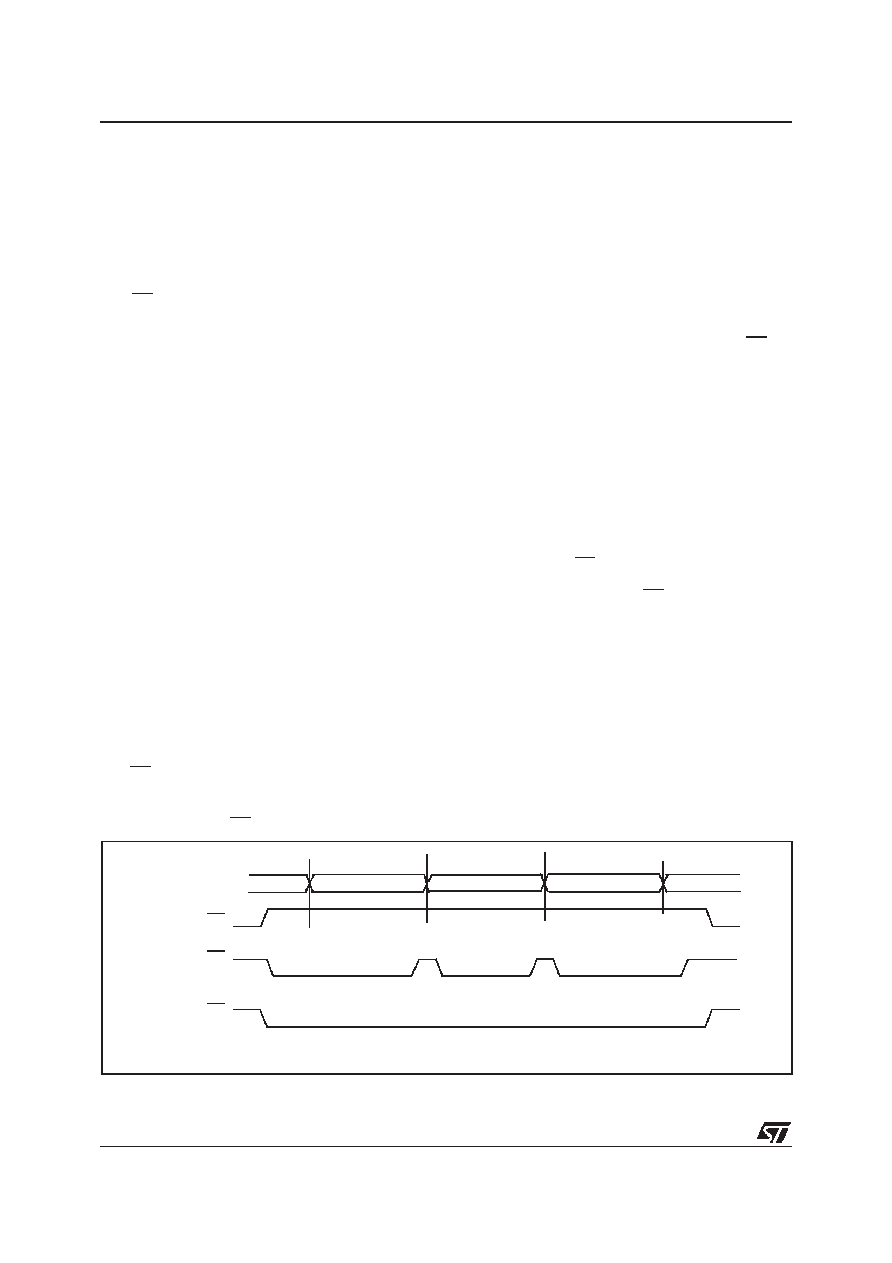

Figure 53. CPHA / SS Timing Diagram

MOSI/MISO

Master SS

Slave SS

(CPHA=0)

Slave SS

(CPHA=1)

Byte 1

Byte 2

Byte 3

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST72F321J9T5 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP44 |

| ST72F324BJ6B6 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP42 |

| ST72F324BK6T6 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP32 |

| ST72F324BK4T6 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PQFP32 |

| ST72F324BJ4B5 | 8-BIT, FLASH, 8 MHz, MICROCONTROLLER, PDIP42 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST72F321J7T6 | 功能描述:8位微控制器 -MCU Flash 48K SPI/SCI/I2 RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F321J7T6TR | 功能描述:8位微控制器 -MCU 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F321J7TA | 功能描述:8位微控制器 -MCU AUTO 8BIT MICRO RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F321J7TAE | 功能描述:8位微控制器 -MCU 8B MCU RoHS:否 制造商:Silicon Labs 核心:8051 處理器系列:C8051F39x 數(shù)據(jù)總線寬度:8 bit 最大時鐘頻率:50 MHz 程序存儲器大小:16 KB 數(shù)據(jù) RAM 大小:1 KB 片上 ADC:Yes 工作電源電壓:1.8 V to 3.6 V 工作溫度范圍:- 40 C to + 105 C 封裝 / 箱體:QFN-20 安裝風(fēng)格:SMD/SMT |

| ST72F321J7TCE | 制造商:STMicroelectronics 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。