- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372294 > ST24LW21B6 IC CONFIG DEVICE 8MBIT 100-PQFP PDF資料下載

參數(shù)資料

| 型號: | ST24LW21B6 |

| 英文描述: | IC CONFIG DEVICE 8MBIT 100-PQFP |

| 中文描述: | I2C串行EEPROM的 |

| 文件頁數(shù): | 13/21頁 |

| 文件大?。?/td> | 152K |

| 代理商: | ST24LW21B6 |

Memory Addressing.

To start communication be-

tween the bus master and the slave ST24xy21, the

master must initiate a START condition. Following

this, the master sends onto the SDA bus line 8 bits

(MSB first) corresponding to the Device Select

code (7 bits) and a READ or WRITE bit. The 4 most

significant bits of the Device Select code are the

device type identifier, corresponding to the I

2

C bus

definition. For these memories the 4 bits are fixed

as 1010b. The following 3 bits are Don’t Care. The

8th bit sent is the read or write bit (RW), this bit is

set to ’1’ for read and ’0’ for write operations. If a

match is found, the corresponding memory will

acknowledge the identification on the SDA bus

during the 9th bit time.

Write Operations

Following a START condition the master sends a

Device Select code with the RW bit set to ’0’. The

memory acknowledges this and waits for a byte

address. After receipt of the byte address the de-

vice again responds with an acknowledge.

In I

2

C bidirectional mode, any write command with

VCLK=0 (for the ST24LC21B and ST24FC21) or

with WC=0 (for the ST24LW21 and ST24FW21) will

not modify data and will be acknowledged on data

bytes, as shown in Figure 12.

Byte Write

. In the Byte Write mode the master

sends one data byte, which is acknowledged by the

memory. The master then terminates the transfer

by generating a STOP condition.

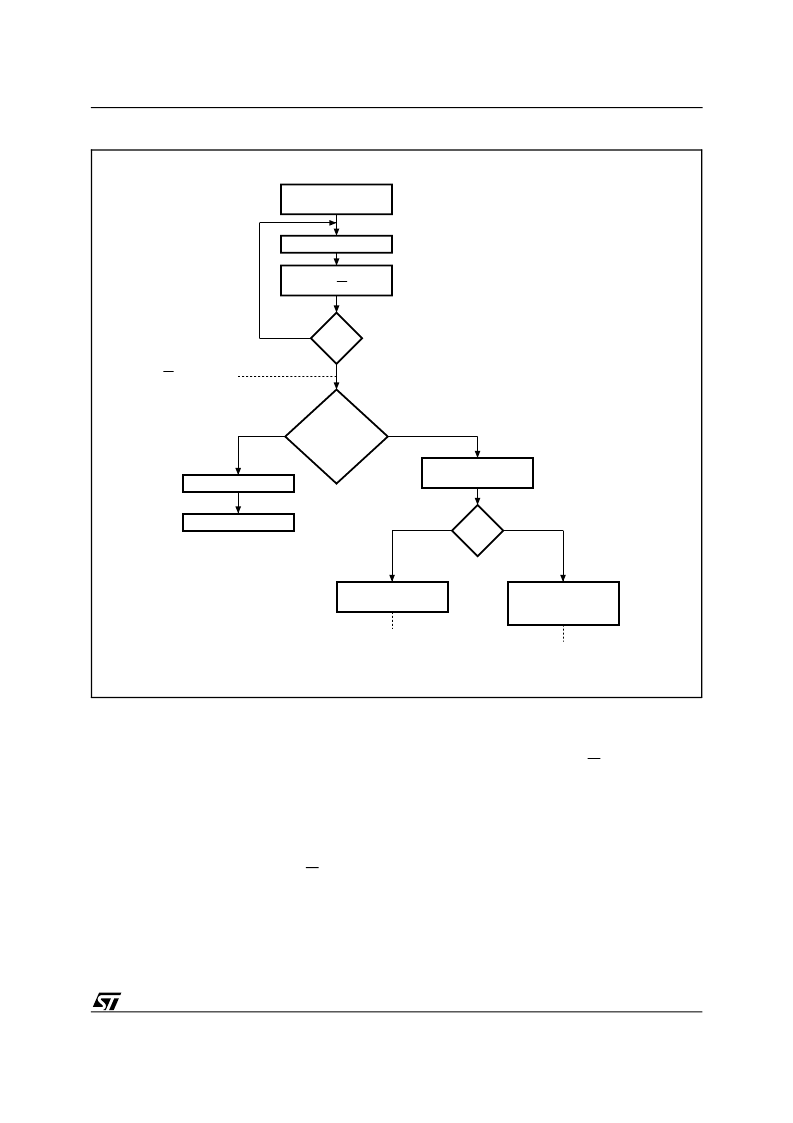

WRITE Cycle

in Progress

AI01099B

Next

Operation is

Addressing the

Memory

START Condition

DEVICE SELECT

with RW = 0

ACK

Returned

YES

NO

YES

NO

ReSTART

STOP

Proceed

WRITE Operation

Proceed

Random Address

READ Operation

Send

Byte Address

First byte of instruction

with RW = 0 already

decoded by ST24xxx

Figure 10. Write Cycle Polling using ACK

13/21

ST24LC21B, ST24LW21, ST24FC21, ST24FW21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST24LW21M1 | Cyclone II FPGA 35K FBGA-672 |

| ST24LW21M6 | Cyclone II FPGA 15K FBGA-256 |

| ST24F | IC CONFIG DEVICE 16MBIT 100-PQFP |

| ST24FC21B1 | MAX II CPLD 570 LE 144-TQFP |

| ST24FC21B6 | IC FLEX 6000 FPGA 16K 208-PQFP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST24LW21B6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY |

| ST24LW21M1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

| ST24LW21M1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY |

| ST24LW21M6 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

| ST24LW21M6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。