- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄372294 > ST24LC21BB6 IC ACEX 1K FPGA 100K 208-PQFP PDF資料下載

參數(shù)資料

| 型號: | ST24LC21BB6 |

| 英文描述: | IC ACEX 1K FPGA 100K 208-PQFP |

| 中文描述: | I2C串行EEPROM的 |

| 文件頁數(shù): | 5/21頁 |

| 文件大小: | 152K |

| 代理商: | ST24LC21BB6 |

I

2

C Bidirectional Mode

The ST24xy21 can be switched from Transmit Only

mode to I

2

C Bidirectional mode by applying a valid

high to low transition on the SCL pin (see Figure 4).

– When the ST24LC21B (or the ST24FC21) is in

the I

2

C Bidirectional mode, the VCLK input

(pin 7) enables (or inhibits) the execution of

any write instruction: if VCLK = 1, write instruc-

tions are executed; if VCLK = 0, write instruc-

tions are not executed.

– When the ST24LW21 (or the ST24FW21) is in

the I

2

C Bidirectional mode, the Write Control

(WC on pin 3) input enables (or inhibits) the

execution of any write instruction: if WC = 1,

write instructions are executed;if WC = 0,

write instructions are not executed.

The ST24xy21 is compatible with the I

2

C standard,

two wire serial interface which uses a bidirectional

data bus and serial clock. The device carries a

built-in 4 bit, unique device identification code

(1010) named Device Select code corresponding

to the I

2

C bus definition.

The ST24xy21 behaves as a slave device in the

I

2

C protocol with all memory operations synchro-

nized by the serial clock SCL. Read and write

operations are initiated by a START condition gen-

erated by the bus master. The START condition is

followed by a stream of 7 bits (Device Select code

1010XXX), plus one read/write bit and terminated

by an acknowledge bit.

When data is written into the memory, the

ST24xy21 responds to the 8 bits received by as-

serting an acknowledge bit during the 9th bit time.

When data is read by the bus master, it must

acknowledges the receipt of the data bytes in the

same way. Data transfers are terminated with a

STOP condition (see READ and WRITE descrip-

tions in the following pages).

Power On Reset: V

CC

lock out write protect

In order to prevent data corruption and inadvertent

write operations during power up, a Power On

Reset (POR) circuit is implemented. Until the V

CC

voltage has reached the POR threshold value

(around 3V), the internal reset is active, all opera-

tions are disabled and the device will not respond

to any command. In the same way, when V

CC

drops

down from the operating voltage to below the POR

threshold value, all operations are disabled and the

device will not respond to any command. A stable

V

CC

must be applied before applying any logic

signal.

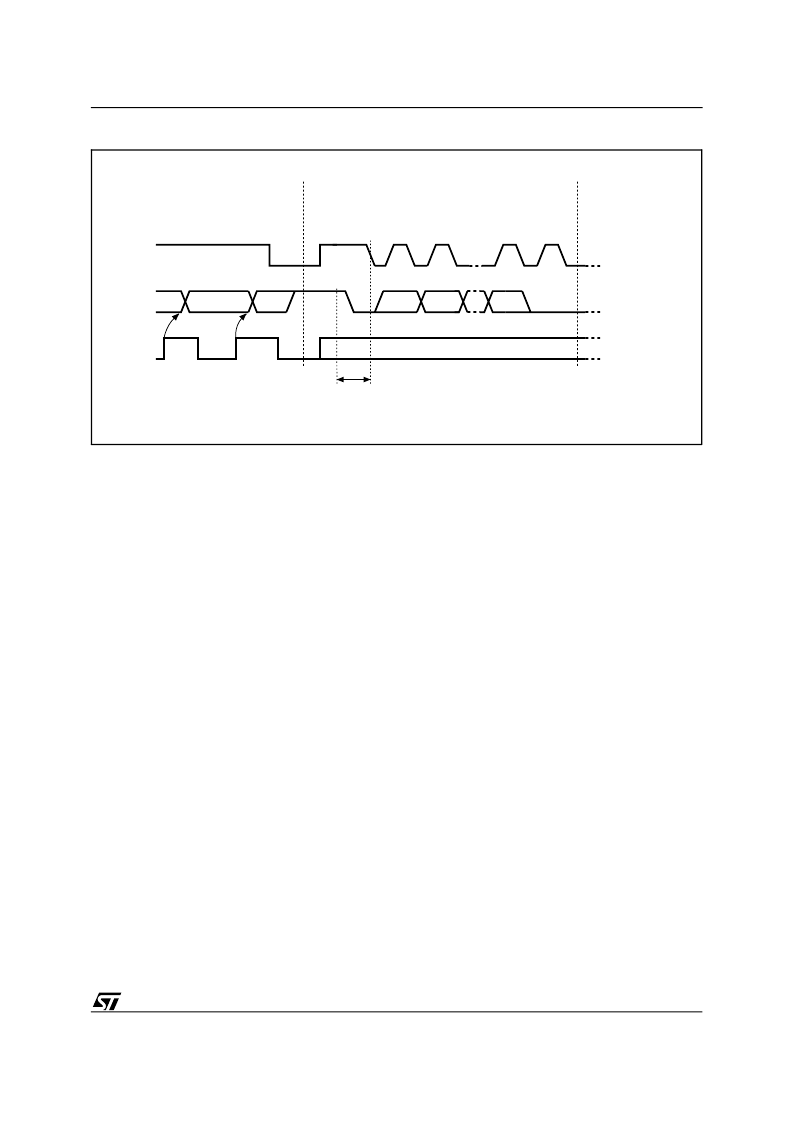

AI01892

SCL

SDA

VCLK

Transmit Only Mode

1

2

8

9

MSB

ACK

START

CONDITION

- Temporary Bi-Directional Mode

(ST24FC21 and ST24FW21)

- Locked Bi-Directional Mode

(ST24LC21B and ST24LW21)

- Locked Bi-Directional

Mode (ST24FC21

and ST24FW21)

Figure 4. Transition from Transmit Only (DDC1) to Bi-directional (DDC2B) Mode Waveforms

5/21

ST24LC21B, ST24LW21, ST24FC21, ST24FW21

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST24LC21BM1 | CONFIGURATION DEVICE, 440KBIT, TQFP32; Memory type:Configuration EPROM; Interface type:Serial; Memory size:430Kbit; Memory configuration:54KB; Frequency:16.7MHz; Temp, op. min:0(degree C); Temp, op. max:70(degree C); Case style:TQFP; RoHS Compliant: Yes |

| ST24LC21BM6 | IC CONFIG DEVICE 16MBIT 100-PQFP |

| ST24LW21B1 | IC CONFIG DEVICE 1.6MBIT 32-TQFP |

| ST24LW21B6 | IC CONFIG DEVICE 8MBIT 100-PQFP |

| ST24LW21M1 | Cyclone II FPGA 35K FBGA-672 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST24LC21BB6TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY |

| ST24LC21BM1 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:I2C Serial EEPROM |

| ST24LC21BM1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:1 Kbit x8 Dual Mode Serial EEPROM for VESA PLUG & PLAY |

| ST24LC21BM6 | 功能描述:電可擦除可編程只讀存儲器 Dual Mode 1K (128x8) RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

| ST24LC21BM6TR | 功能描述:電可擦除可編程只讀存儲器 Dual Mode 1K (128x8) RoHS:否 制造商:Atmel 存儲容量:2 Kbit 組織:256 B x 8 數(shù)據(jù)保留:100 yr 最大時鐘頻率:1000 KHz 最大工作電流:6 uA 工作電源電壓:1.7 V to 5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-8 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。