- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98142 > SST85LP1004B-M-C-LFTE IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 PDF資料下載

參數(shù)資料

| 型號(hào): | SST85LP1004B-M-C-LFTE |

| 元件分類: | 存儲(chǔ)控制器/管理單元 |

| 英文描述: | IDE COMPATIBLE, FLASH MEMORY DRIVE CONTROLLER, PBGA91 |

| 封裝: | 14 X 24 MM, 1.30 MM HEIGHT, ROHS COMPLIANT, BGA-91 |

| 文件頁數(shù): | 35/36頁 |

| 文件大?。?/td> | 910K |

| 代理商: | SST85LP1004B-M-C-LFTE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁當(dāng)前第35頁第36頁

2010 Silicon Storage Technology, Inc.

S71420-01-000

04/10

8

4 GByte NANDrive

SST85LP1004B

Advance Information

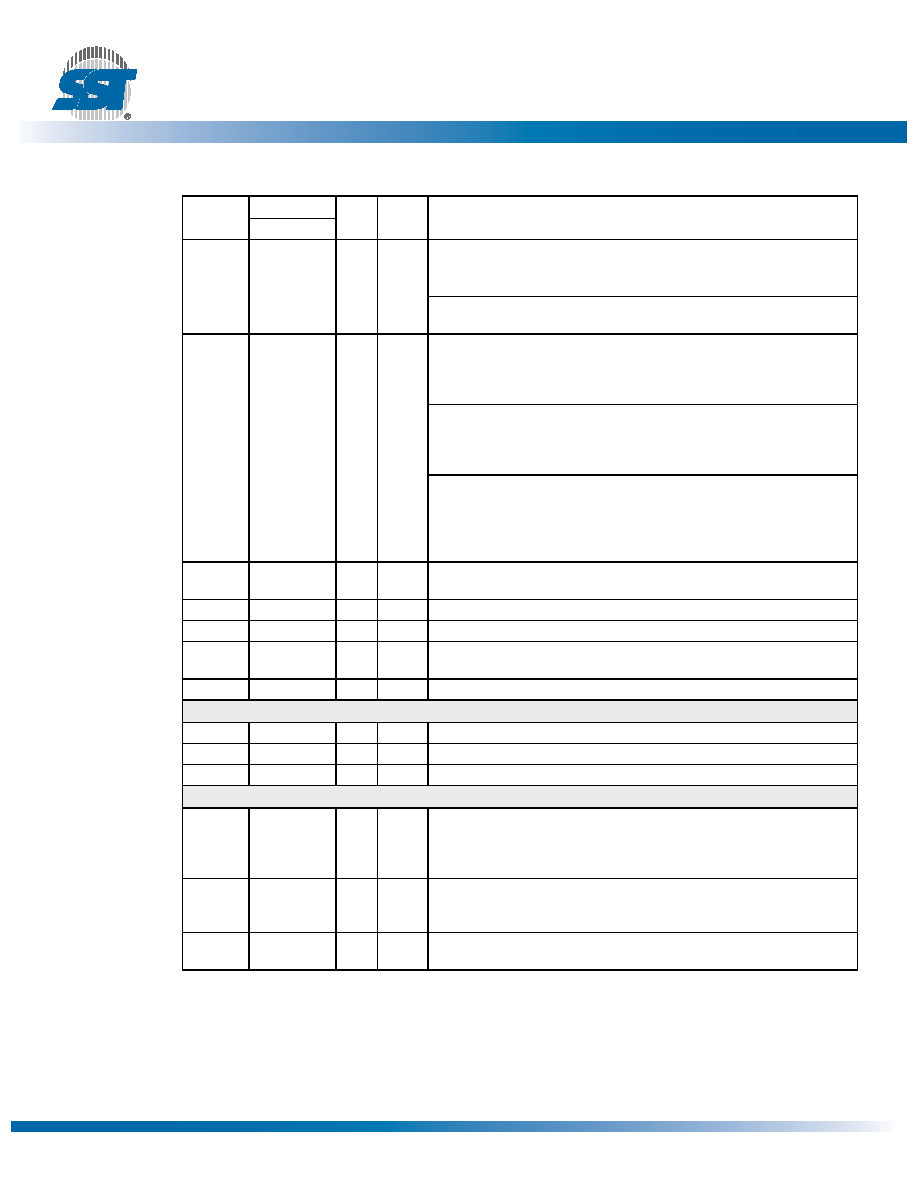

IOWR#

H9

I

I2Z

IOWR#: This is an I/O Write Strobe generated by the host. When Ultra

DMA mode is not active, this signal is used to clock I/O data into

the device. (This pin supports two functions)

STOP: When Ultra DMA mode protocol is active, the assertion of this

signal causes the termination of the Ultra DMA burst

IORDY

J4

O

O2

IORDY: When in PIO mode, the device is not ready to respond to a data

transfer request. This signal is negated to extend the Host transfer cycle

from the assertion of IORD# or IOWR#. However, it is never negated by

this controller. (This pin supports three functions)

DDMARDY#: When Ultra DMA mode DMA Write is active, this signal is

asserted by the device to indicate that the device is ready to receive

Ultra DMA data-out bursts. The device may negate DDMARDY# to

pause an Ultra DMA transfer.

DSTROBE: When Ultra DMA mode DMA Read is active, this signal is

the data-in strobe generated by the device. Both the rising and falling

edges of DSTROBE cause data to be latched by the host. The device

may stop generating DSTROBE edges to pause an Ultra DMA data-in

burst.

IOCS16#

J8

O

O3

This output signal is asserted low when the device is indicating a word

data transfer cycle.

INTRQ

J2

O

O2

This signal is the active high Interrupt Request to the host.

PDIAG#

K9

I/O

I1U/O2 The Pass Diagnostic signal in the Master/Slave handshake protocol.

DASP#

D9

I/O

I1U/O4 The Drive Active/Slave Present signal in the Master/Slave handshake

protocol.

RESET#

E4

I

I2U

This input pin is the active low hardware reset from the host.

Serial Communication Interface (SCI)

SCIDOUT

D8

O

O2

SCI interface data output

SCIDIN

D7

I

I1U

SCI interface data input

SCICLK

E7

I

I1D

SCI interface clock

Miscellaneous

WP#/PD#

F6

I

I2U

The WP#/PD# pin can be used for either the Write Protect mode or

Power-down mode, but only one mode is active at any time. The Write

Protect or Power-down modes can be selected through the host com-

mand. The Write Protect mode is the factory default setting.

VSS1

G4, G6, G7,

K4, K6, K7,

J9

PWR

Ground

VDD1

E2, E9, K5,

L5, M2, M9

PWR

VDD (3.3V)

Table 1: Pin Assignments (Continued) (2 of 3)

Symbol

Pin No.

Pin

Type

I/O

Type

Name and Functions

91-LBGA

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SST89C58-33-I-TQJE | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PQFP44 |

| SST89E516RD-40-C-QIF | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, QCC40 |

| SST89E516RD2-40-C-NJE | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PQCC44 |

| SST89E52RD-40-C-PI | 8-BIT, FLASH, 40 MHz, MICROCONTROLLER, PDIP40 |

| SST89V58RD-33-C-PI | 8-BIT, FLASH, 33 MHz, MICROCONTROLLER, PDIP40 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SST85LP1016B-M-C-FTE | 功能描述:閃存 16G NAND 3.3V Commercial RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲(chǔ)類型:Flash 存儲(chǔ)容量:2 MB 結(jié)構(gòu):256 K x 8 定時(shí)類型: 接口類型:SPI 訪問時(shí)間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| SST88VP1107 | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:All-in-OneMemory |

| SST88VP1107-80-5C-LBSE | 功能描述:組合存儲(chǔ)器 NOR/NAND/PSRAM 80MHz 2.7V Commercial RoHS:否 制造商:Microchip Technology 組織:512 K x 16 電源電壓-最大: 電源電壓-最小: 最大工作溫度:+ 85 C 最小工作溫度:- 20 C 封裝 / 箱體:LFBGA-48 封裝:Tray |

| SST88VP1107-80-5W-LBSE | 功能描述:組合存儲(chǔ)器 NOR/NAND/PSRAM 80MHz 2.7V Wireless RoHS:否 制造商:Microchip Technology 組織:512 K x 16 電源電壓-最大: 電源電壓-最小: 最大工作溫度:+ 85 C 最小工作溫度:- 20 C 封裝 / 箱體:LFBGA-48 封裝:Tray |

| SST89C54 | 制造商:SST 制造商全稱:Silicon Storage Technology, Inc 功能描述:FlashFlex51 MCU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。