- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376414 > SN74LS174N (MOTOROLA INC) Low Distortion Attenuator Pin Diode in Surface Mount SOD-323 Package PDF資料下載

參數(shù)資料

| 型號(hào): | SN74LS174N |

| 廠商: | MOTOROLA INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | Low Distortion Attenuator Pin Diode in Surface Mount SOD-323 Package |

| 中文描述: | LS SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDIP16 |

| 封裝: | PLASTIC, DIP-16 |

| 文件頁數(shù): | 1/3頁 |

| 文件大?。?/td> | 75K |

| 代理商: | SN74LS174N |

5-1

FAST AND LS TTL DATA

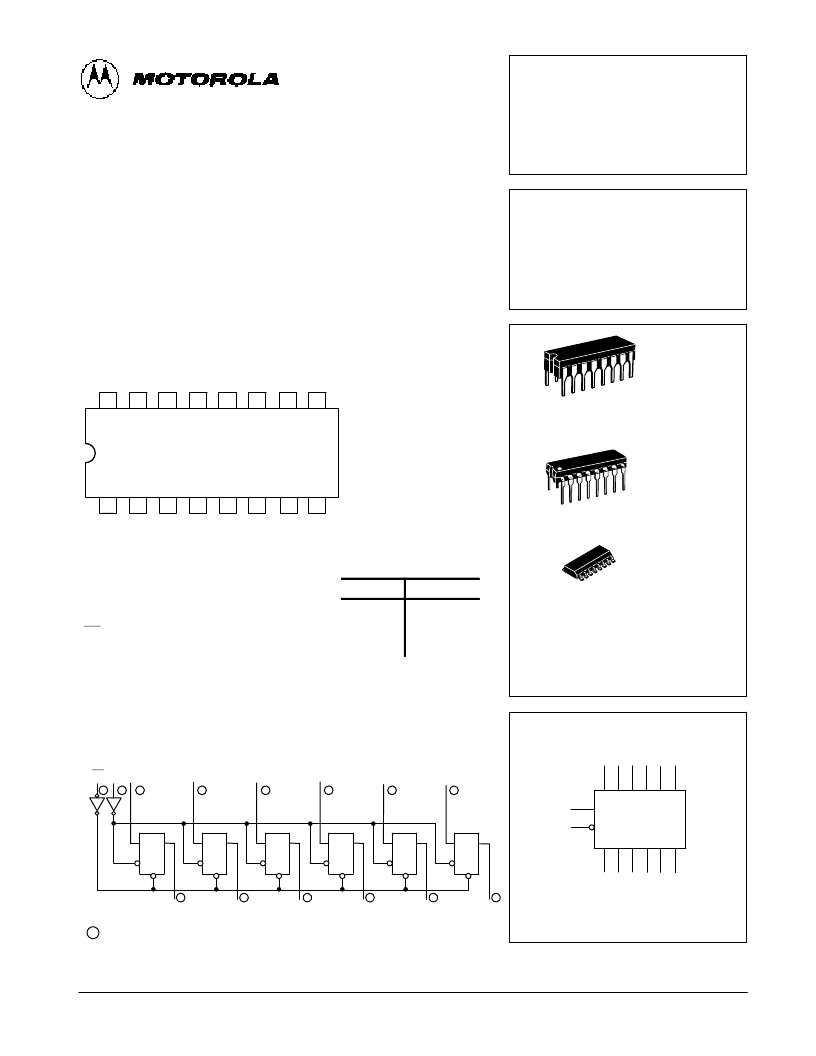

HEX D FLIP-FLOP

The LSTTL/MSI SN54/74LS174 is a high speed Hex D Flip-Flop. The

device is used primarily as a 6-bit edge-triggered storage register. The

information on the D inputs is transferred to storage during the LOW to HIGH

clock transition. The device has a Master Reset to simultaneously clear all

flip-flops. The LS174 is fabricated with the Schottky barrier diode process for

high speed and is completely compatible with all Motorola TTL families.

Edge-Triggered D-Type Inputs

Buffered-Positive Edge-Triggered Clock

Asynchronous Common Reset

Input Clamp Diodes Limit High Speed Termination Effects

NOTE:

The Flatpak version

has the same pinouts

(Connection Diagram) as

the Dual In-Line Package.

CONNECTION DIAGRAM DIP

(TOP VIEW)

14

13

12

11

10

9

1

2

Q0

3

D0

4

D1

5

Q1

6

D2

7

Q2

16

15

8

VCC

MR

Q5

D5

D4

Q4

Q3

D3

CP

GND

PIN NAMES

LOADING

(Note a)

HIGH

LOW

D0–D5

CP

MR

Q0–Q5

NOTES:

a. 1 TTL Unit Load (U.L.) = 40

μ

A HIGH/1.6 mA LOW.

b. The Output LOW drive factor is 2.5 U.L. for Military (54) and 5 U.L. for Commercial (74)

b.

Temperature Ranges.

Data Inputs

Clock (Active HIGH Going Edge) Input

Master Reset (Active LOW) Input

Outputs (Note b)

0.5 U.L.

0.5 U.L.

0.5 U.L.

10 U.L.

0.25 U.L.

0.25 U.L.

0.25 U.L.

5 (2.5) U.L.

LOGIC DIAGRAM

D

Q

CPCD

Q5

Q4

Q3

Q2

Q1

Q0

CP

D5

D4

D3

D2

D1

D0

MR

14

2

6

7

3

4

5

9

11

12

10

13

15

D

Q

CPCD

D

Q

CPCD

D

Q

CPCD

D

Q

CPCD

D

Q

CPCD

1

VCC = PIN 16

GND = PIN 8

= PIN NUMBERS

SN54/74LS174

HEX D FLIP-FLOP

LOW POWER SCHOTTKY

J SUFFIX

CERAMIC

CASE 620-09

N SUFFIX

PLASTIC

CASE 648-08

16

1

16

1

ORDERING INFORMATION

SN54LSXXXJ

SN74LSXXXN

SN74LSXXXD

Ceramic

Plastic

SOIC

16

1

D SUFFIX

SOIC

CASE 751B-03

LOGIC SYMBOL

VCC = PIN 16

GND = PIN 8

D5

D4

D3

D2

D1

D0

CP

MR

Q0

9

1

3 4

6 11 13 14

Q2

Q1

Q3Q4Q5

2

5

7 10 12 15

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74LS175D | High Gain, High Linearity Active Bias Low Noise Amplifier |

| SN54LS175 | QUAD D FLIP-FLOP |

| SN54LS175J | QUAD D FLIP-FLOP |

| SN74LS175N | High Gain, High Linearity Active Bias Low Noise Amplifier |

| SN74LS181N | 4-BIT ARITHMETIC LOGIC UNIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LS174N | 制造商:Texas Instruments 功能描述:Flip Flop Logic IC |

| SN74LS174NDS82 | 制造商:Motorola 功能描述:74LS174N |

| SN74LS174NE4 | 功能描述:觸發(fā)器 Hex D-Type Flip-Flop With Clear RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| SN74LS174NS | 制造商:Texas Instruments 功能描述: |

| SN74LS174NSR | 功能描述:觸發(fā)器 Hex D-Type Flip-Flop With Clear RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時(shí)間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。